# HIGH CURRENT SWITCHING REGULATORS

- 4 A OUTPUT CURRENT

- 5.1 V TO 40 V OUTPUT VOLTAGE RANGE

- 0 TO 100 % DUTY CYCLE RANGE

- PRECISE (±2 %) ON-CHIP REFERENCE

- SWITCHING FREQUENCY UP TO 200 KHz

- VERY HIGH EFFICIENCY (UP TO 90 %)

- VERY FEW EXTERNAL COMPONENTS

- SOFT START

- RESET OUTPUT

- EXTERNAL PROGRAMMABLE LIMITING CURRENT (L296P)

- CONTROL CIRCUIT FOR CROWBAR SCR

- INPUT FOR REMOTE INHIBIT AND SYNCHRONUS PWM

- THERMAL SHUTDOWN

#### DESCRIPTION

The L296 and L296P are stepdown power switching regulators delivering 4 A at a voltage variable from 5.1 V to 40 V.

Features of the devices include soft start, remote inhibit, thermal protection, a reset output for microprocessors and a PWM comparator input for synchronization in multichip configurations.

The L296P incudes external programmable limiting current.

The L296 and L296P are mounted in a 15-lead Multiwatt® plastic power package and requires very few external components.

Efficient operation at switching frequencies up to 200 KHz allows a reduction in the size and cost of external filter components. A voltage sense input and SCR drive output are provided for optional crowbar overvoltage protection with an external SCR.

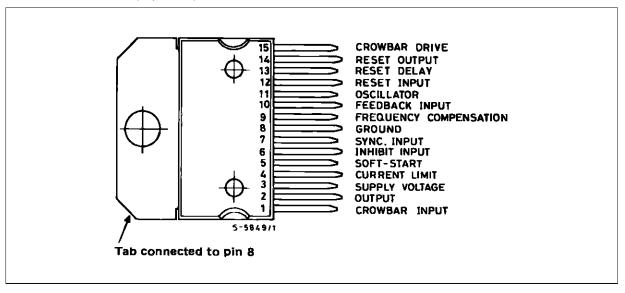

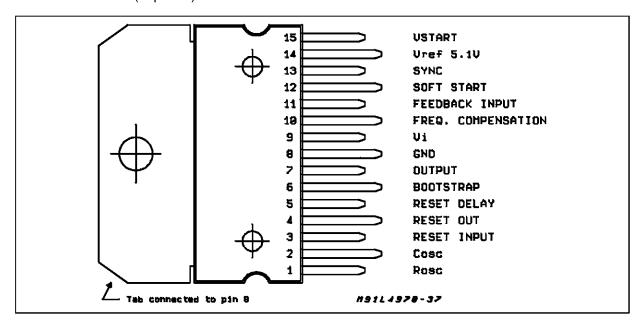

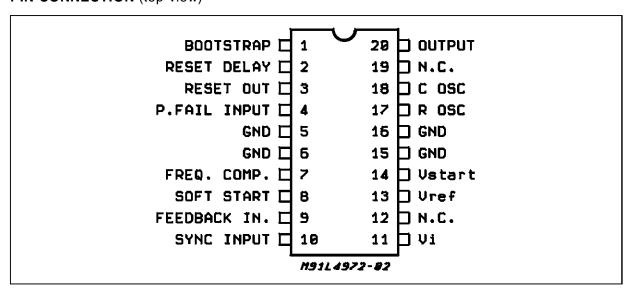

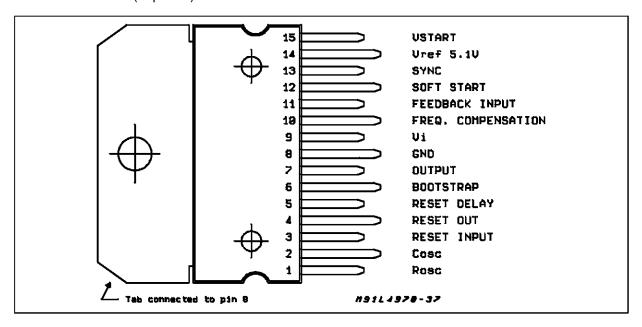

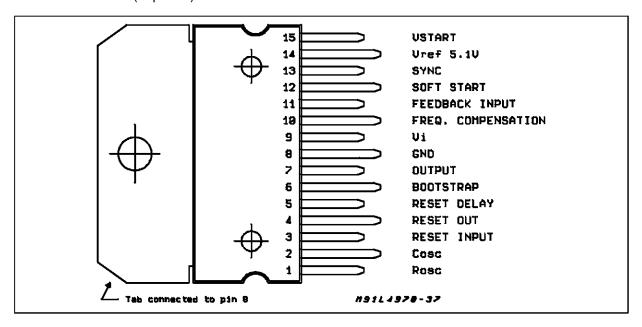

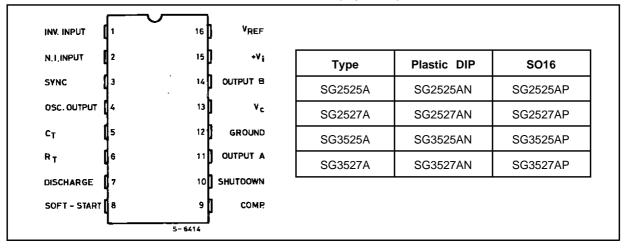

#### **PIN CONNECTION** (top view)

April 1993 1/21

#### **PIN FUNCTIONS**

| N° | Name                      | Function                                                                                                                                                                                                                                                                                                |

|----|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | CROWBAR INPUT             | Voltage Sense Input for Crowbar Overvoltage Protection. Normally connected to the feedback input thus triggering the SCR when V <sub>out</sub> exceeds nominal by 20 %. May also monitor the input and a voltage divider can be added to increase the threshold. Connected to ground when SCR not used. |

| 2  | OUTPUT                    | Regulator Output                                                                                                                                                                                                                                                                                        |

| 3  | SUPPLY VOLTAGE            | Unrergulated Voltage Input. An internal Regulator Powers the L296s Internal Logic.                                                                                                                                                                                                                      |

| 4  | CURRENT LIMIT             | A resistor connected between this terminal and ground sets the current limiter threshold. If this terminal is left unconnected the threshold is internally set (see electrical characteristics).                                                                                                        |

| 5  | SOFT START                | Soft Start Time Constant. A capacitor is connected between this terminal and ground to define the soft start time constant. This capacitor also determines the average short circuit output current.                                                                                                    |

| 6  | INHIBIT INPUT             | TTL – Level Remote Inhibit. A logic high level on this input disables the device.                                                                                                                                                                                                                       |

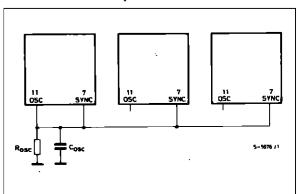

| 7  | SYNC INPUT                | Multiple L296s are synchronized by connecting the pin 7 inputs together and omitting the oscillator RC network on all but one device.                                                                                                                                                                   |

| 8  | GROUND                    | Common Ground Terminal                                                                                                                                                                                                                                                                                  |

| 9  | FREQUENCY<br>COMPENSATION | A series RC network connected between this terminal and ground determines the regulation loop gain characteristics.                                                                                                                                                                                     |

| 10 | FEEDBACK INPUT            | The Feedback Terminal on the Regulation Loop. The output is connected directly to this terminal for 5.1V operation; it is connected via a divider for higher voltages.                                                                                                                                  |

| 11 | OSCILLATOR                | A parallel RC networki connected to this terminal determines the switching frequency. This pin must be connected to pin 7 input when the internal oscillator is used.                                                                                                                                   |

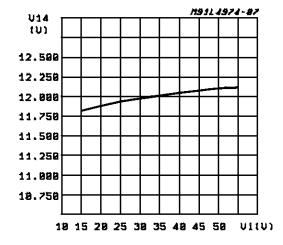

| 12 | RESET INPUT               | Input of the Reset Circuit. The threshold is roughly 5 V. It may be connected to the feedback point or via a divider to the input.                                                                                                                                                                      |

| 13 | RESET DELAY               | A capacitor connected between this terminal and ground determines the reset signal delay time.                                                                                                                                                                                                          |

| 14 | RESET OUTPUT              | Open collector reset signal output. This output is high when the supply is safe.                                                                                                                                                                                                                        |

| 15 | CROWBAR OUTPUT            | SCR gate drive output of the crowbar circuit.                                                                                                                                                                                                                                                           |

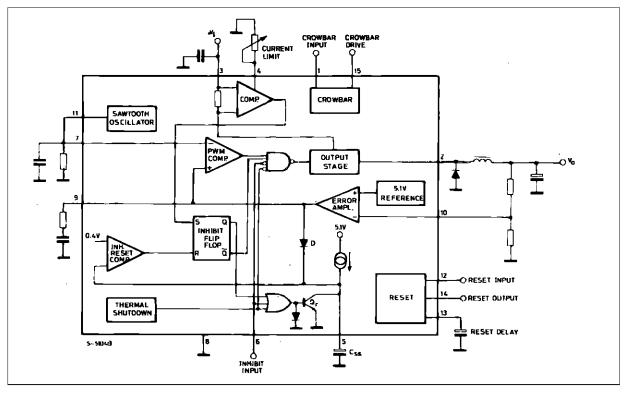

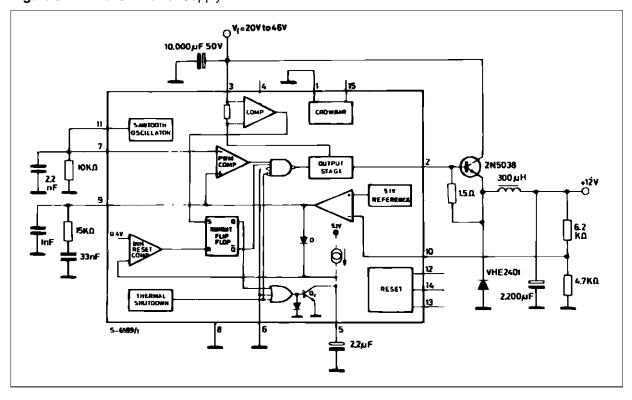

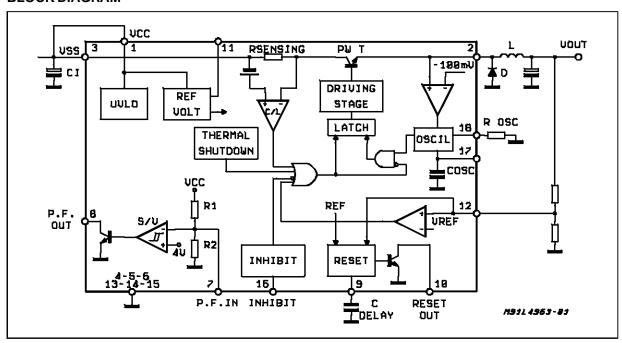

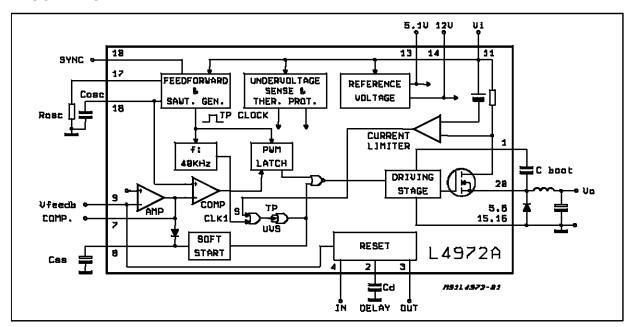

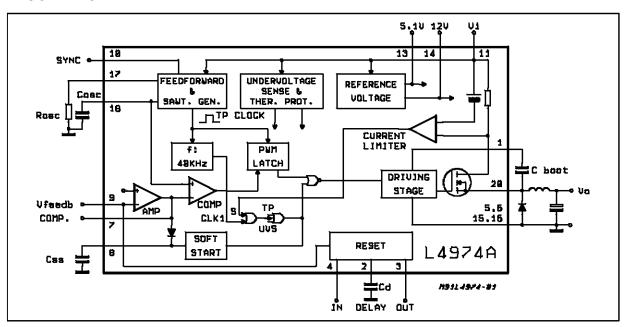

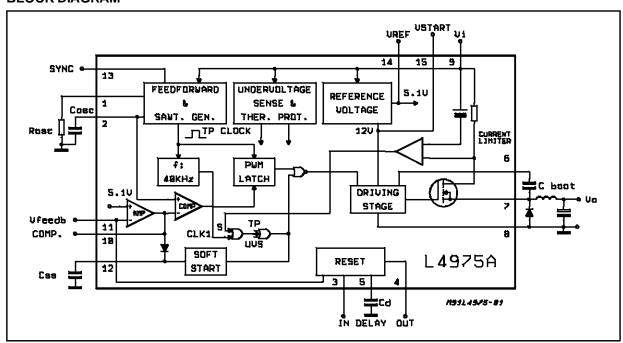

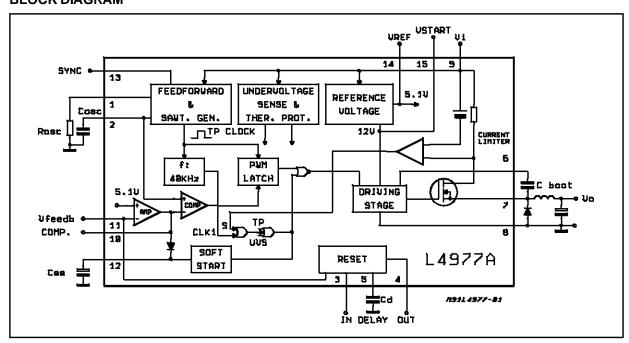

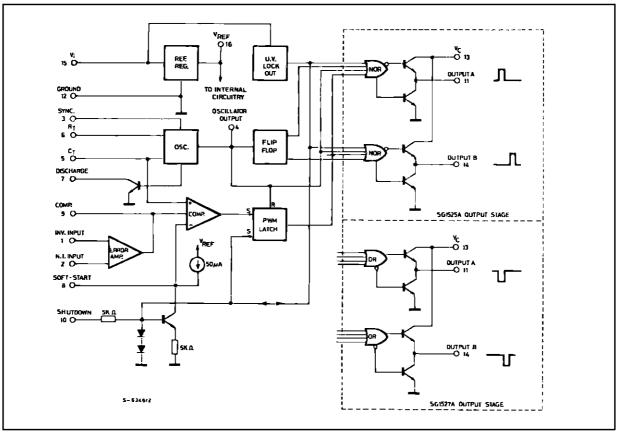

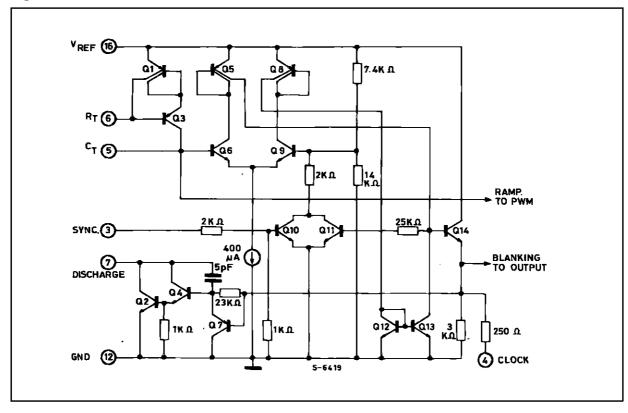

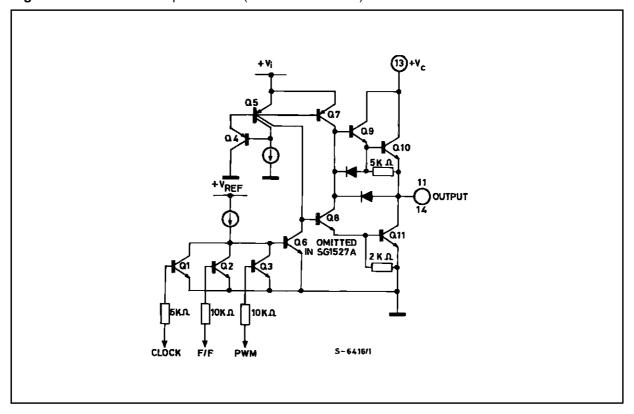

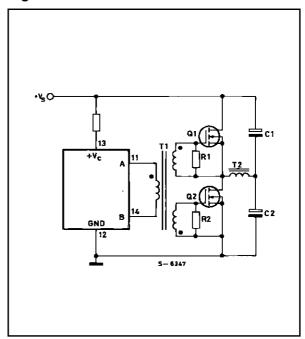

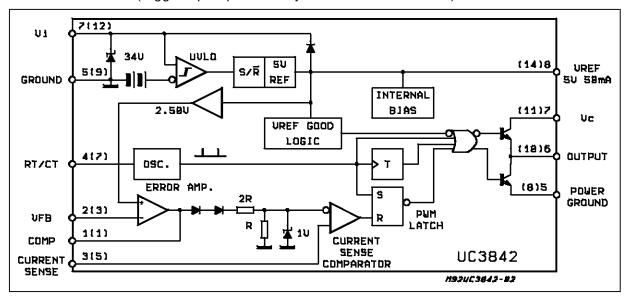

# **BLOCK DIAGRAM**

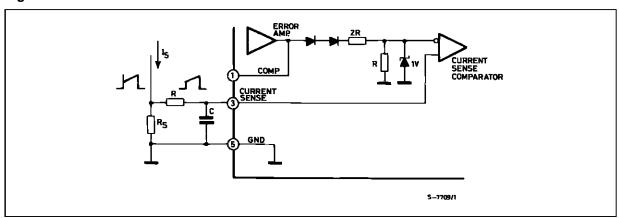

#### CIRCUIT OPERATION

(refer to the block diagram)

The L296 and L296P are monolithic stepdown switching regulators providing output voltages from 5.1V to 40V and delivering 4A.

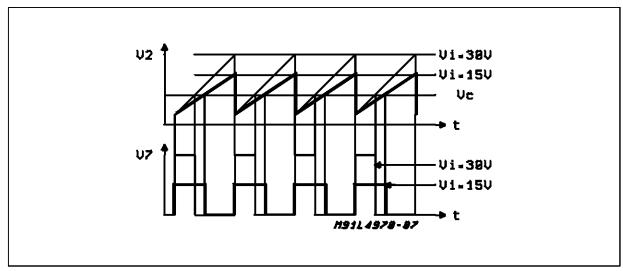

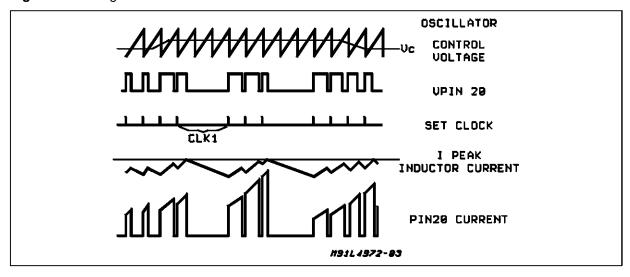

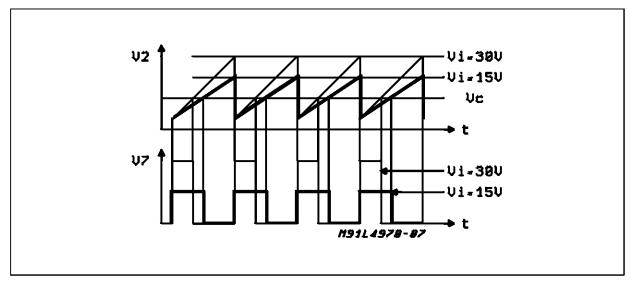

The regulation loop consists of a sawtooth oscillator, error amplifier, comparator and the output stage. An error signal is produced by comparing the output voltage with a precise 5.1V on-chip reference (zener zap trimmed to  $\pm 2\%$ ). This error signal is then compared with the sawtooth signal to generate the fixed frequency pulse width modulated pulses which drive the output stage. The gain and frequency stability of the loop can be adjusted by an external RC network connected to pin 9. Closing the loop directly gives an output voltage of 5.1V. Higher voltages are obtained by inserting a voltage divider.

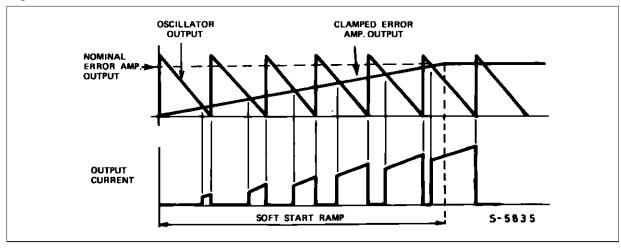

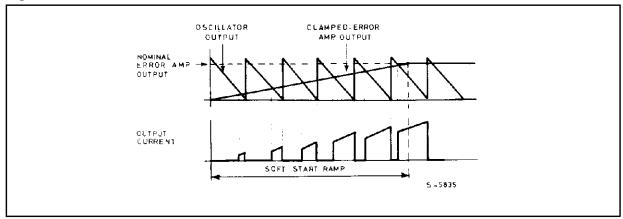

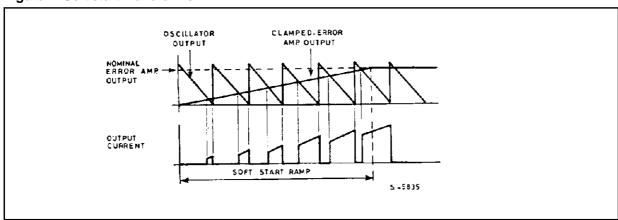

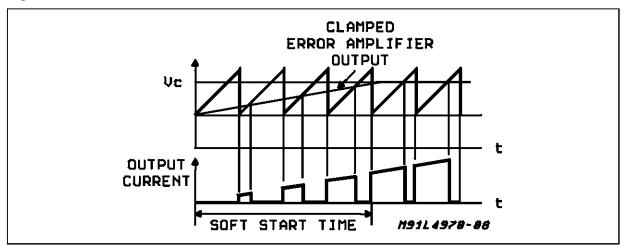

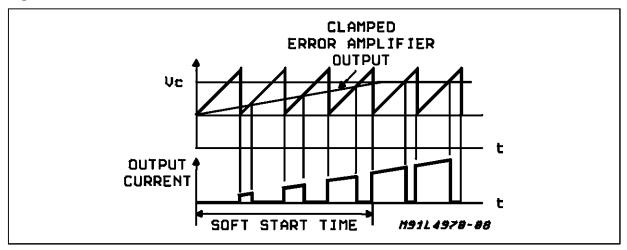

Output overcurrents at switch on are prevented by the soft start function. The error amplifier output is initially clamped by the external capacitor Css and allowed to rise, linearly, as this capacitor is charged by a constant current source.

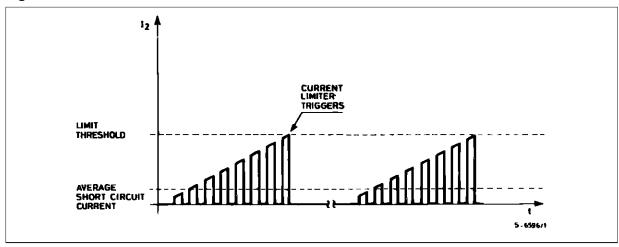

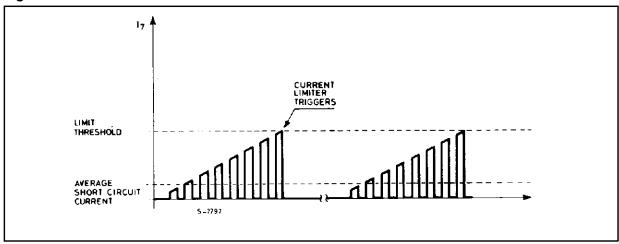

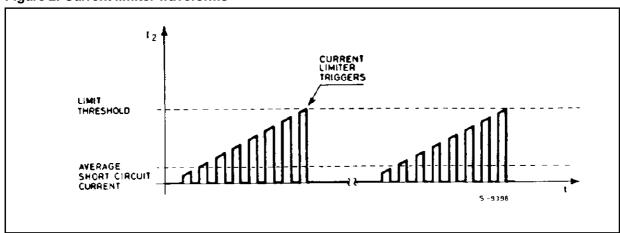

Output overload protection is provided in the form of a current limiter. The load current is sensed by an internal metal resistor connected to a comparator. When the load current exceeds a preset threshold this comparator sets a flip flop which disables the output stage and discharges the soft start capacitor. A second comparator resets the flip flop when the voltage across the soft start capacitor has fallen to

0.4V. The output stage is thus re-enabled and the output voltage rises under control of the soft start network. If the overload condition is still present the limiter will trigger again when the threshold current is reached. The average short circuit current is limited to a safe value by the dead time introduced by the soft start network.

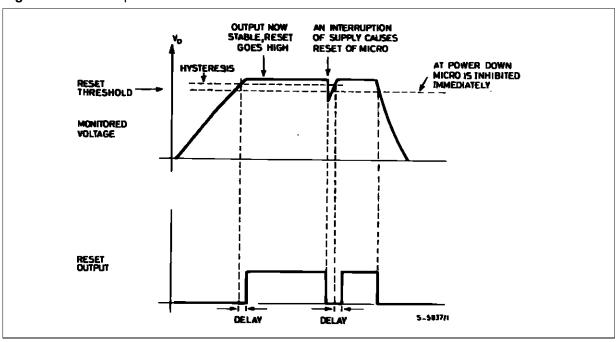

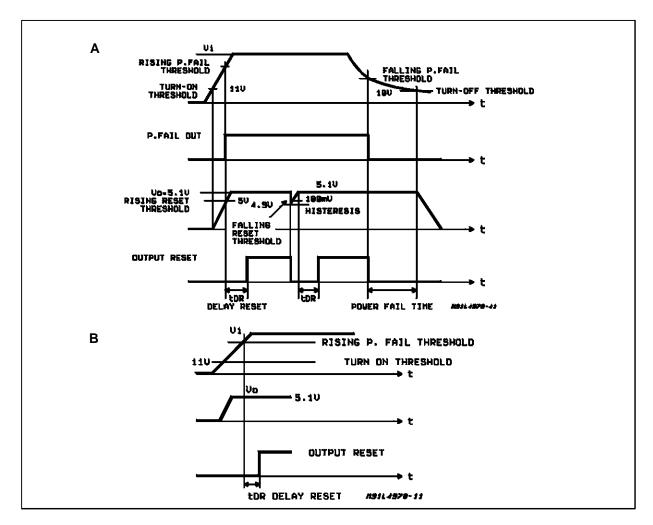

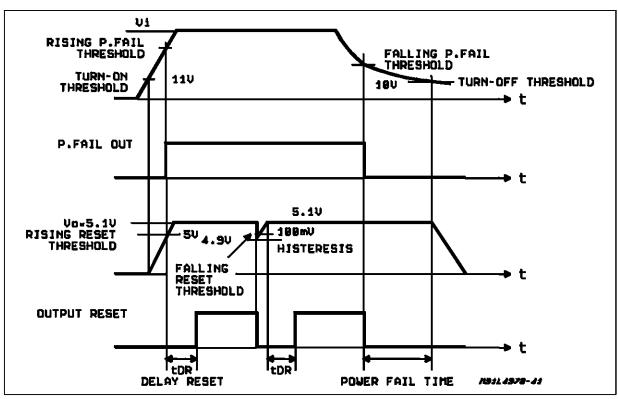

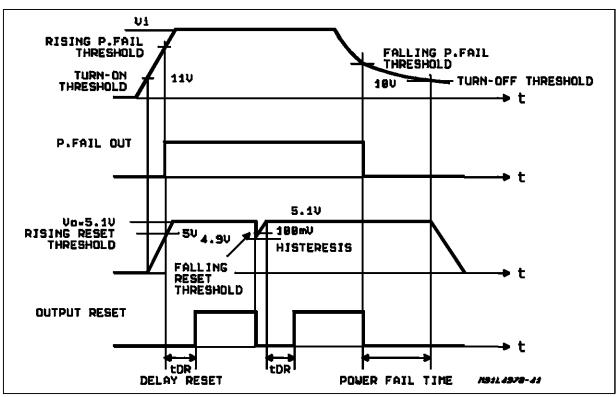

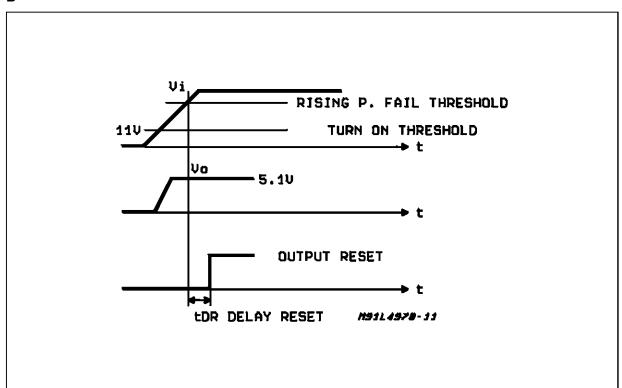

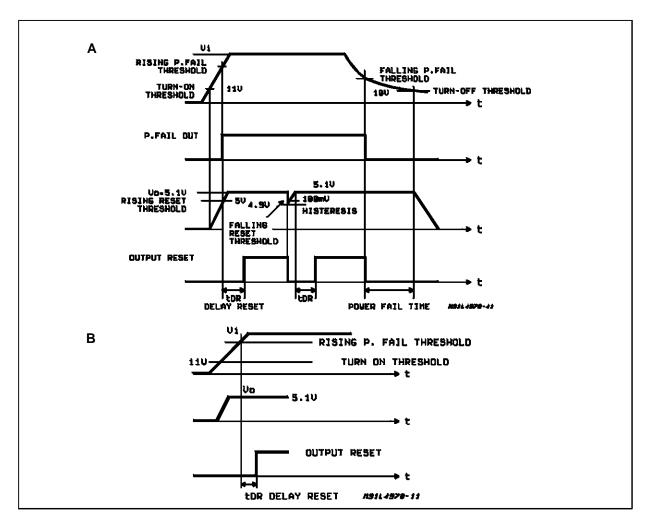

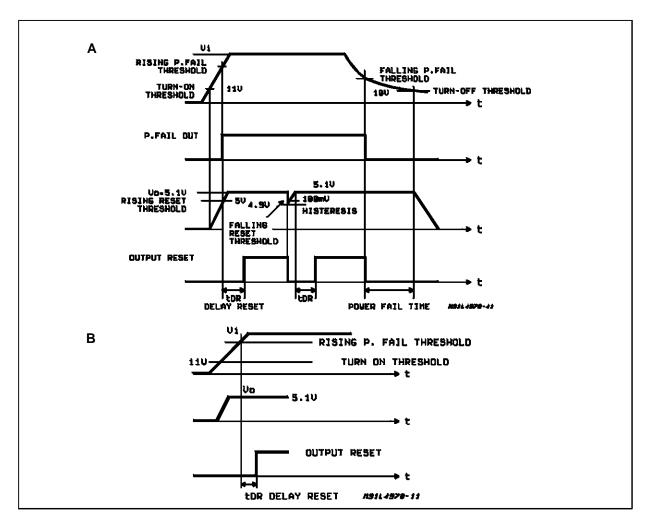

The reset circuit generates an output signal when the supply voltage exceeds a threshold programmed by an external divider. The reset signal is generated with a delay time programmed by an external capacitor. When the supply falls below the threshold the reset output goes low immediately. The reset output is an open collector.

The scrowbar circuit senses the output voltage and the crowbar output can provide a current of 100mA to switch on an external SCR. This SCR is triggered when the output voltage exceeds the nominal by 20%. There is no internal connection between the output and crowbar sense input therefore the crowbar can monitor either the input or the output.

A TTL - level inhibit input is provided for applications such as remote on/off control. This input is activated by high logic level and disables circuit operation. After an inhibit the L296 restarts under control of the soft start network.

The thermal overload circuit disables circuit operation when the junction temperature reaches about 150 °C and has hysteresis to prevent unstable conditions.

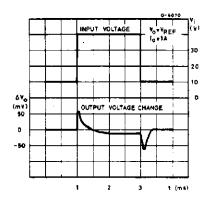

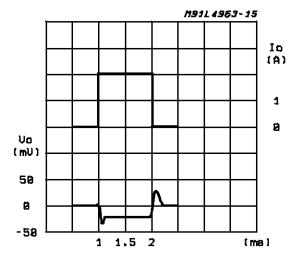

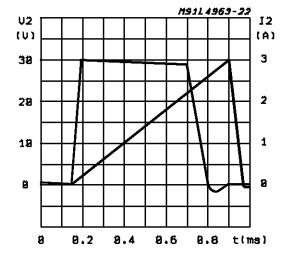

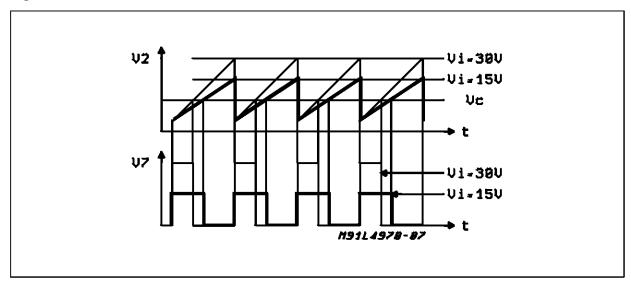

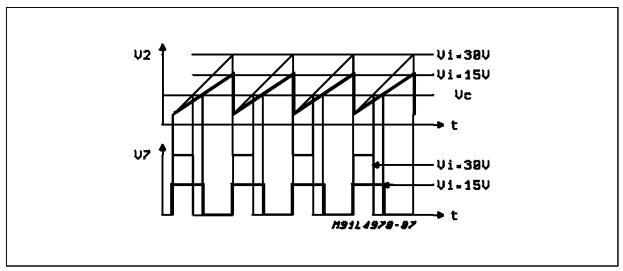

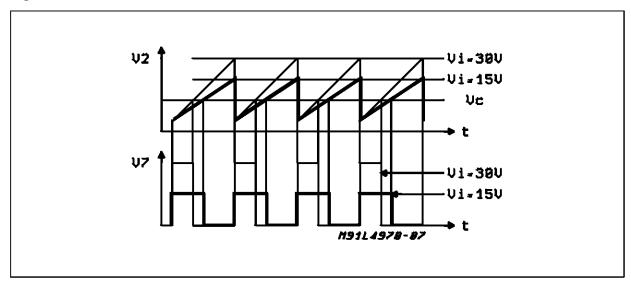

Figure 2: Soft Start Waveforms

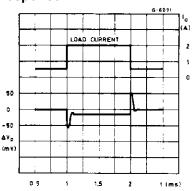

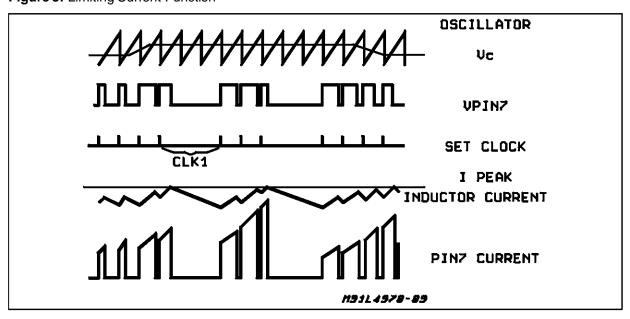

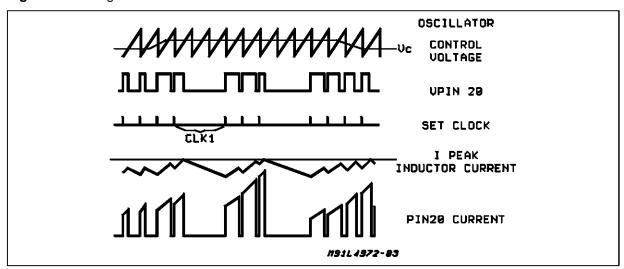

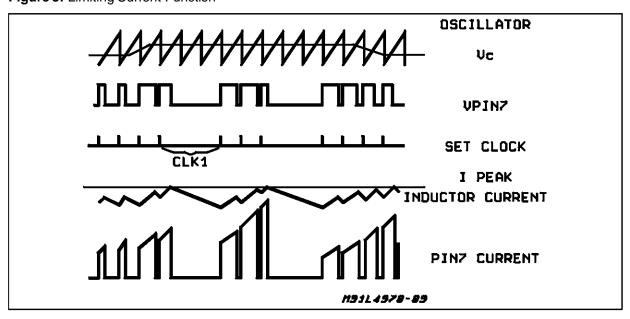

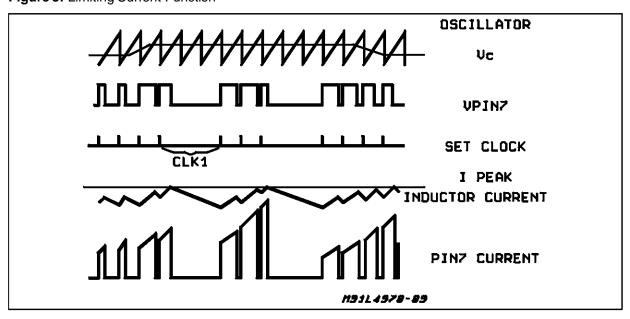

Figure 3: Current Limiter Waveforms

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                                                                              | Parameter                                                        | Value       | Unit |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------|------|

| Vi                                                                                  | Input Voltage (pin 3)                                            | 50          | V    |

| $V_i - V_2$                                                                         | Input to Output Voltage Difference                               | 50          | V    |

| V <sub>2</sub>                                                                      | Output DC Voltage Output Peak Voltage at t = 0.1 µsec f = 200KHz | - 1<br>- 7  | V    |

| V <sub>1</sub> , V <sub>12</sub>                                                    | Voltage at Pins 1, 12                                            | 10          | V    |

| V <sub>15</sub>                                                                     | Voltage at Pin 15                                                | 15          | V    |

| V <sub>4</sub> , V <sub>5</sub> , V <sub>7</sub> , V <sub>9</sub> , V <sub>13</sub> | Voltage at Pins 4, 5, 7, 9 and 13                                | 5.5         | V    |

| V <sub>10</sub> , V <sub>6</sub>                                                    | Voltage at Pins 10 and 6                                         | 7           | V    |

| V <sub>14</sub>                                                                     | Voltage at Pin 14 (I <sub>14</sub> ≤ 1 mA)                       | Vi          |      |

| l <sub>9</sub>                                                                      | Pin 9 Sink Current                                               | 1           | mA   |

| I <sub>11</sub>                                                                     | Pin 11 Source Current                                            | 20          | mA   |

| I <sub>14</sub>                                                                     | Pin 14 Sink Current (V <sub>14</sub> < 5 V)                      | 50          | mA   |

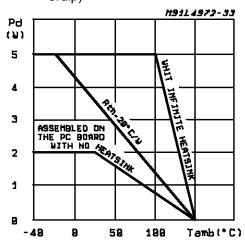

| P <sub>tot</sub>                                                                    | Power Dissipation at T <sub>case</sub> ≤ 90 °C                   | 20          | W    |

| T <sub>j</sub> , T <sub>stg</sub>                                                   | Junction and Storage Temperature                                 | - 40 to 150 | °C   |

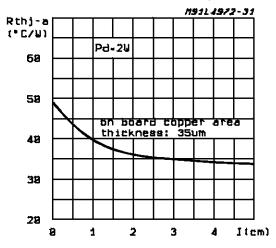

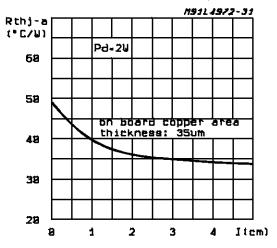

# THERMAL DATA

| Symbol                 | Parameter                                | Value | Unit |

|------------------------|------------------------------------------|-------|------|

| R <sub>th j-case</sub> | Thermal Resistance Junction-case Max.    | 3     | °C/W |

| R <sub>th j-amb</sub>  | Thermal Resistance Junction-ambient Max. | 35    | °C/W |

# **ELECTRICAL CHARACTERISTICS**

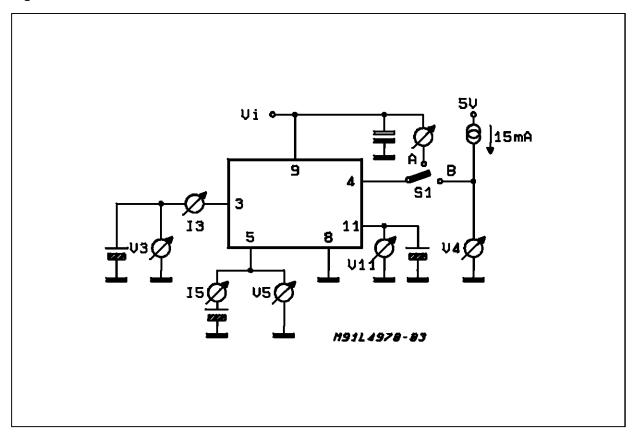

(refer to the test circuits  $T_j = 25^{\circ}C$ ,  $V_i = 35V$ , unless otherwise specified)

| Symbol                          | Parameter                                            | Test Conditions                                                                                                                                               | Min.             | Тур.     | Max.       | Unit     | Fig.   |

|---------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------|------------|----------|--------|

| DYNAMIC                         | CHARACTERISTICS (pin 6 to GND                        | unless otherwise specified)                                                                                                                                   |                  |          |            |          |        |

| Vo                              | Output Voltage Range                                 | $V_i = 46V, I_0 = 1A$                                                                                                                                         | V <sub>ref</sub> |          | 40         | V        | 4      |

| Vi                              | Input Voltage Range                                  | $V_0 = V_{ref}$ to 36V, $I_0 \le 3A$                                                                                                                          | 9                |          | 46         | V        | 4      |

| Vi                              | Input Voltage Range                                  | Note (1), $V_0 = V_{REF}$ to 36V $I_0 = 4A$                                                                                                                   |                  |          | 46         | V        | 4      |

| $\Delta V_o$                    | Line Regulation                                      | $V_i$ =10V to 40V, $V_o = V_{ref}$ , $I_o = 2A$                                                                                                               |                  | 15       | 50         | mV       | 4      |

| ΔVo                             | Load Regulation                                      | $\label{eq:Vo} \begin{array}{l} V_o = V_{ref} \\ I_o = 2A \text{ to } 4A \\ I_o = 0.5A \text{ to } 4A \end{array}$                                            |                  | 10<br>15 | 30<br>45   | mV       | 4      |

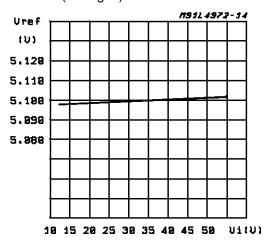

| V <sub>ref</sub>                | Internal Reference Voltage (pin 10)                  | $V_i = 9V$ to 46V, $I_o = 2A$                                                                                                                                 | 5                | 5.1      | 5.2        | V        | 4      |

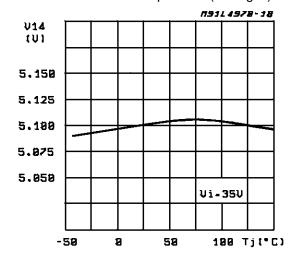

| $\frac{\DeltaV_{ref}}{\DeltaT}$ | Average Temperature Coefficient of Reference Voltage | $T_j = 0$ °C to 125°C, $I_0 = 2A$                                                                                                                             |                  | 0.4      |            | mV/°C    |        |

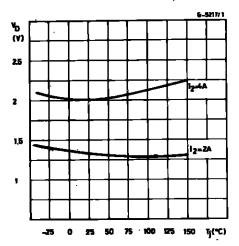

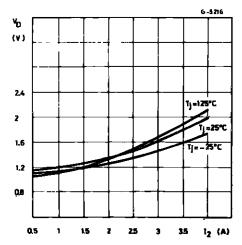

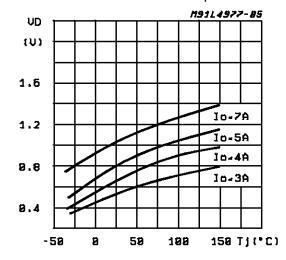

| V <sub>d</sub>                  | Dropout Voltage Between Pin 2 and Pin 3              | $I_0 = 4A$ $I_0 = 2A$                                                                                                                                         |                  | 2<br>1.3 | 3.2<br>2.1 | >>       | 4<br>4 |

| I <sub>2L</sub>                 | Current Limiting Threshold (pin 2)                   | L296 - Pin 4 Open, $V_i = 9V$ to 40V, $V_o = V_{ref}$ to 36V                                                                                                  | 4.5              |          | 7.5        | Α        | 4      |

|                                 |                                                      | $\begin{array}{l} \text{L296P - V}_i = 9 \text{V to 40V, V}_o = \text{V}_{ref} \\ \text{Pin 4 Open} \\ \text{R}_{\text{lim}} = 22 \text{k}\Omega \end{array}$ | 5<br>2.5         |          | 7<br>4.5   | Α        | 4      |

| I <sub>SH</sub>                 | Input Average Current                                | $V_i = 46V$ , Output Short-circuited                                                                                                                          |                  | 60       | 100        | mA       | 4      |

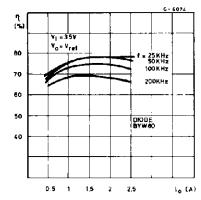

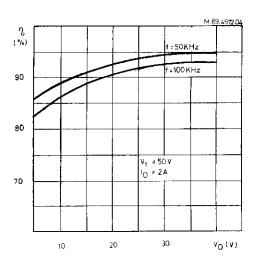

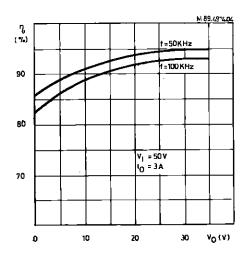

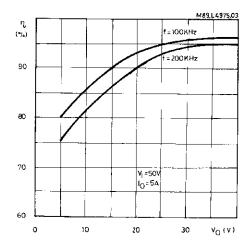

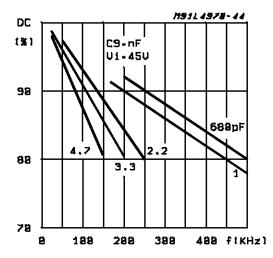

| η                               | Efficiency                                           | $\begin{array}{l} I_o = 3 \text{ A} \\ V_o = V_{ref} \\ V_o = 12V \end{array}$                                                                                |                  | 75<br>85 |            | %        | 4      |

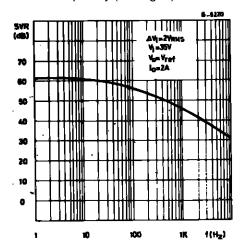

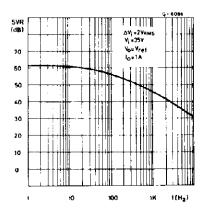

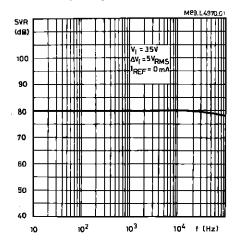

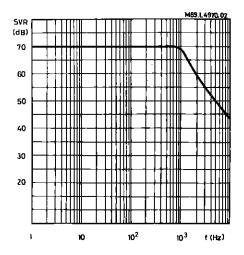

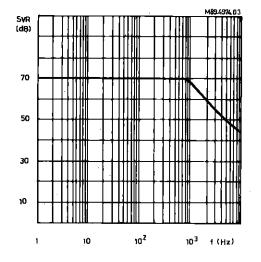

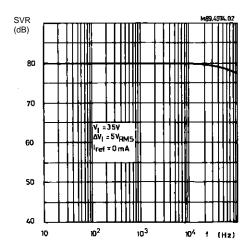

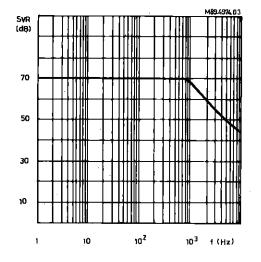

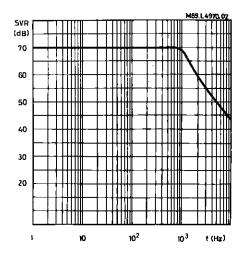

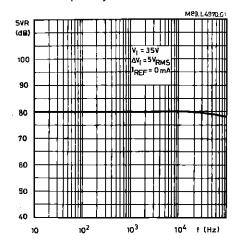

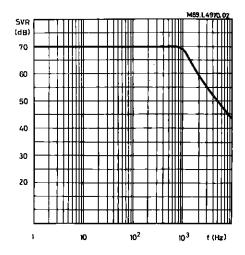

| SVR                             | Supply Voltage Ripple Rejection                      | $\begin{array}{l} \Delta V_i = 2 \; V_{rms},  f_{ripple} = 100 Hz \\ V_o = V_{ref}, \; I_o = 2 A \end{array}$                                                 | 50               | 56       |            | dB       | 4      |

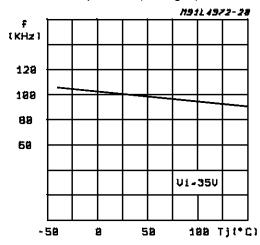

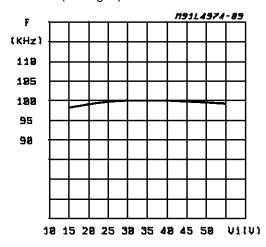

| f                               | Switching Frequency                                  |                                                                                                                                                               | 85               | 100      | 115        | kHz      | 4      |

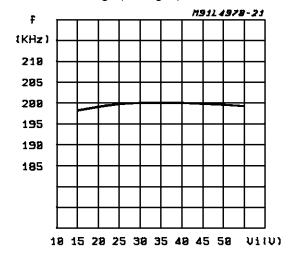

| $\frac{\Delta f}{\Delta V_i}$   | Voltage Stability of Switching Frequency             | $V_i = 9V \text{ to } 46V$                                                                                                                                    |                  | 0.5      |            | %        | 4      |

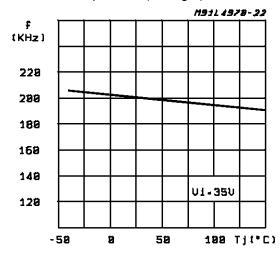

| $\frac{\Delta f}{\Delta T_j}$   | Temperature Stability of Switching Frequency         | $T_j = 0$ °C to 125°C                                                                                                                                         |                  | 1        |            | %        | 4      |

| f <sub>max</sub>                | Maximum Operating Switching Frequency                | $V_o = V_{ref}$ , $I_o = 1A$                                                                                                                                  | 200              |          |            | kHz      | _      |

| T <sub>sd</sub>                 | Thermal Shutdown Junction Temperature                | Note (2)                                                                                                                                                      | 135              | 145      |            | °C       | _      |

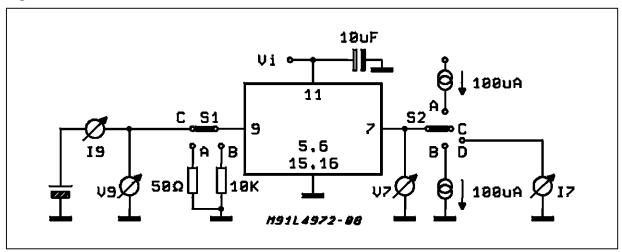

| DC CHAR                         | ACTERISTICS                                          |                                                                                                                                                               |                  |          |            |          |        |

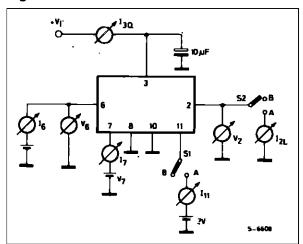

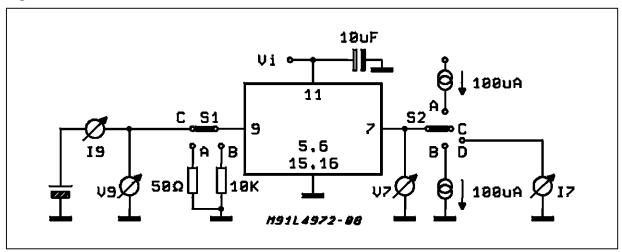

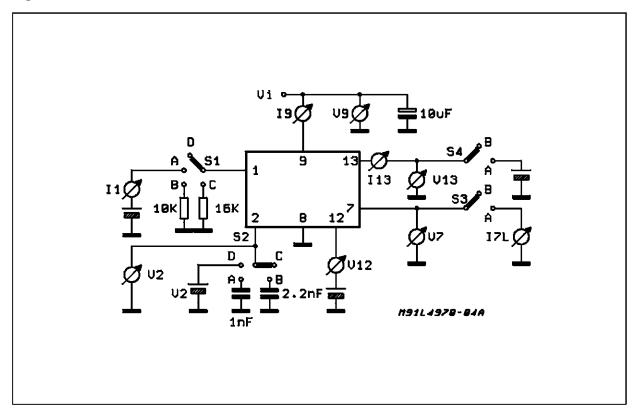

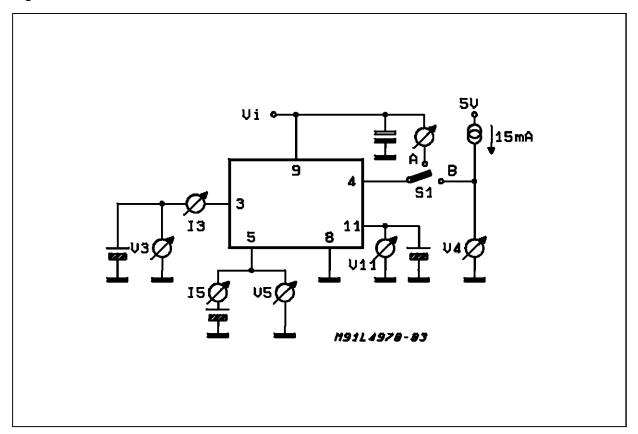

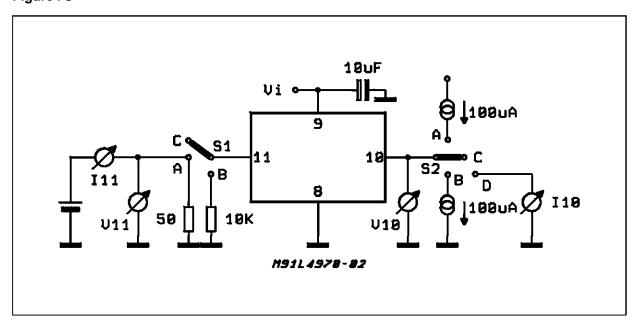

| I <sub>3Q</sub>                 | Quiescent Drain Current                              | $V_i = 46V, V_7 = 0V, S1 : B, S2 : B$<br>$V_6 = 0V$<br>$V_6 = 3V$                                                                                             |                  |          | 66<br>30   | 85<br>40 | mA     |

| - I <sub>2L</sub>               | Output Leakage Current                               | $V_i = 46V, V_6 = 3V, S1 : B, S2 : A, V_7 = 0V$                                                                                                               |                  |          |            | 2        | mA     |

Note

(1) : Using min. 7 A schottky diode.

(2) : Guaranteed by design, not 100 % tested in production.

# **ELECTRICAL CHARACTERISTICS** (continued)

| Symbol                                 | Parameter                                                      | Test Conditions                                                                                                 | Min.                       | Тур.                       | Max.                       | Unit     | Fig.     |

|----------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|----------------------------|----------|----------|

| SOFT STA                               | ART                                                            |                                                                                                                 |                            |                            |                            |          |          |

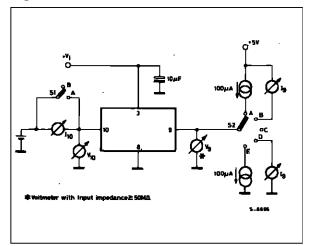

| I <sub>5 so</sub>                      | Source Current                                                 | $V_6 = 0V, V_5 = 3V$                                                                                            | 80                         | 130                        | 150                        | μΑ       | 6b       |

| I <sub>5 si</sub>                      | Sink Current                                                   | $V_6 = 3V, V_5 = 3V$                                                                                            | 50                         | 70                         | 120                        | μΑ       | 6b       |

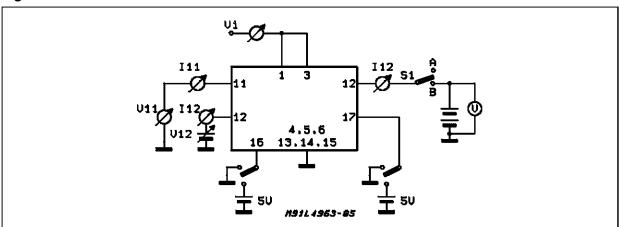

| NHIBIT                                 |                                                                |                                                                                                                 |                            |                            |                            |          |          |

| V <sub>6L</sub><br>V <sub>6H</sub>     | Input Voltage<br>Low Level<br>High Level                       | $V_i = 9V \text{ to } 46V, V_7 = 0V, S1 : B, S2 : B$                                                            | - 0.3<br>2                 |                            | 0.8<br>5.5                 | V        | 6a       |

| – I <sub>6L</sub><br>– I <sub>6H</sub> | Input Current<br>with Input Voltage<br>Low Level<br>High Level | $ \begin{array}{l} V_i = 9V \ to \ 46V, \ V_7 = 0V, \\ S1 : B, \ S2 : B \\ V_6 = 0.8V \\ V_6 = 2V \end{array} $ |                            |                            | 10<br>3                    | μА       | 6a       |

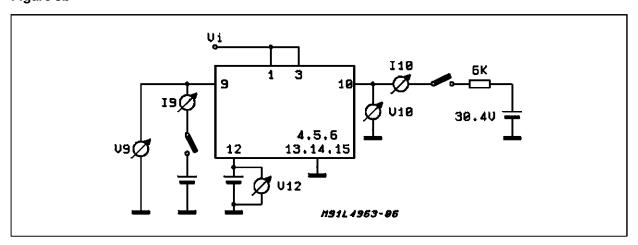

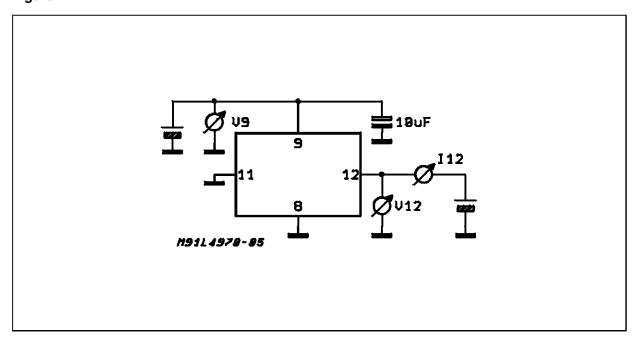

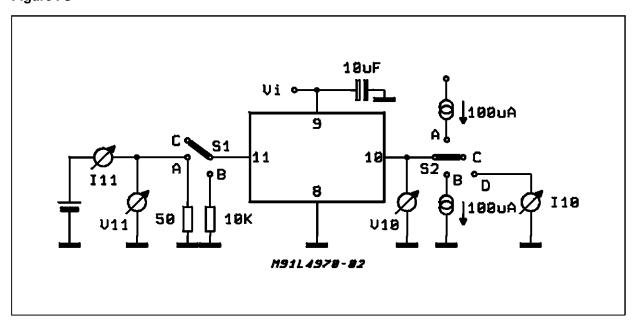

| ERROR A                                | MPLIFIER                                                       |                                                                                                                 |                            |                            |                            |          |          |

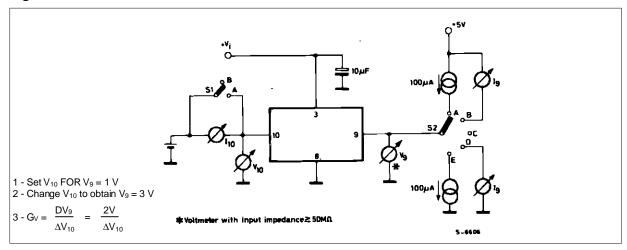

| V <sub>9H</sub>                        | High Level Output Voltage                                      | $V_{10} = 4.7V, I_9 = 100 \mu A, S1 : A, S2 : A$                                                                | 3.5                        |                            |                            | V        | 6c       |

| V <sub>9L</sub>                        | Low Level Output Voltage                                       | $V_{10} = 5.3V$ , $I_9 = 100\mu A$ , $S1:A,S2:E$                                                                |                            |                            | 0.5                        | V        | 6c       |

| I <sub>9 si</sub>                      | Sink Output Current                                            | V <sub>10</sub> = 5.3V, S1 : A, S2 : B                                                                          | 100                        | 150                        |                            | μΑ       | 6c       |

| - I <sub>9 so</sub>                    | Source Output Current                                          | V <sub>10</sub> = 4.7V, S1 : A, S2 : D                                                                          | 100                        | 150                        |                            | μΑ       | 6c       |

| I <sub>10</sub>                        | Input Bias Current                                             | V <sub>10</sub> = 5.2V, S1 : B<br>V <sub>10</sub> = 6.4V, S1 : B, L296P                                         |                            | 2 2                        | 10<br>10                   | μA<br>μA | 6c<br>6c |

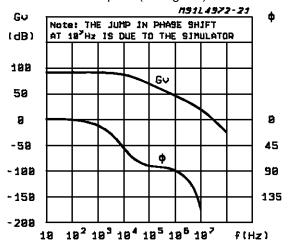

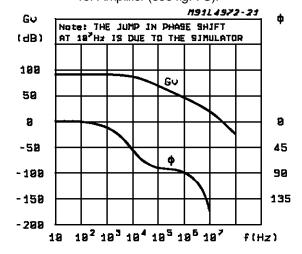

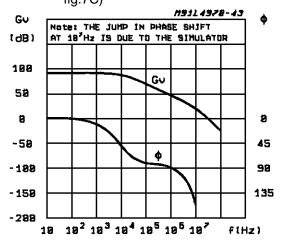

| Gν                                     | DC Open Loop Gain                                              | $V_9 = 1V \text{ to } 3V, \text{ S1 : A, S2 : C}$                                                               | 46                         | 55                         |                            | dB       | 6c       |

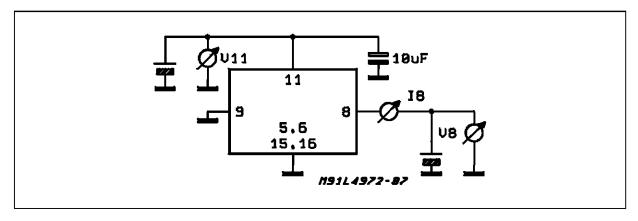

| OSCILLAT                               | TOR AND PWM COMPARAT                                           | OR                                                                                                              |                            |                            |                            |          |          |

| - I <sub>7</sub>                       | Input Bias Current of PWM Comparator                           | $V_7 = 0.5V$ to 3.5V                                                                                            |                            |                            | 5                          | μА       | 6a       |

| - I <sub>11</sub>                      | Oscillator Source Current                                      | V <sub>11</sub> = 2V, S1 : A, S2 : B                                                                            | 5                          |                            |                            | mA       |          |

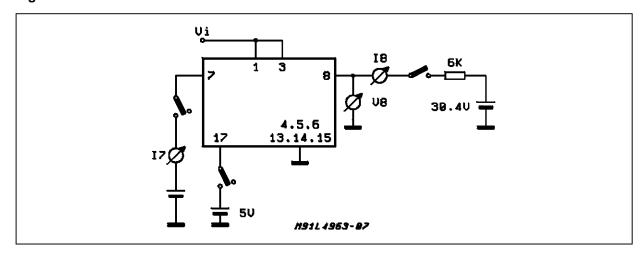

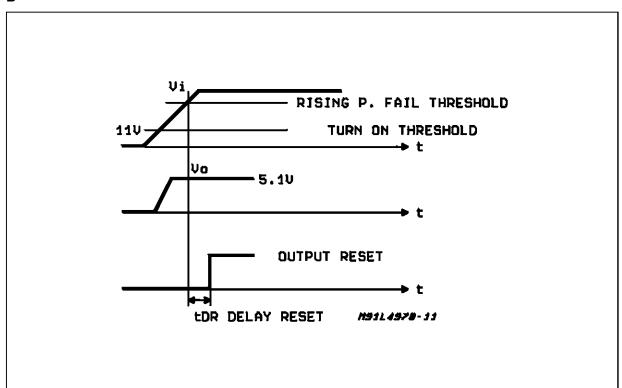

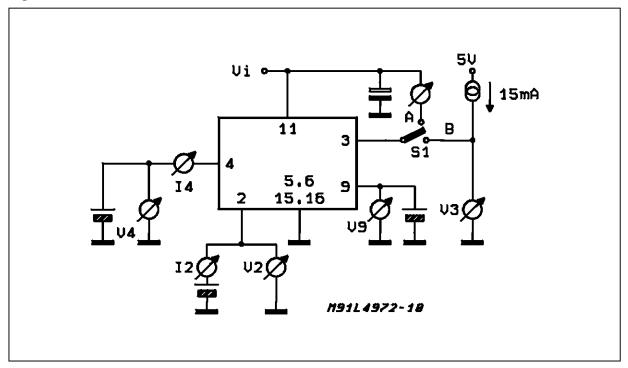

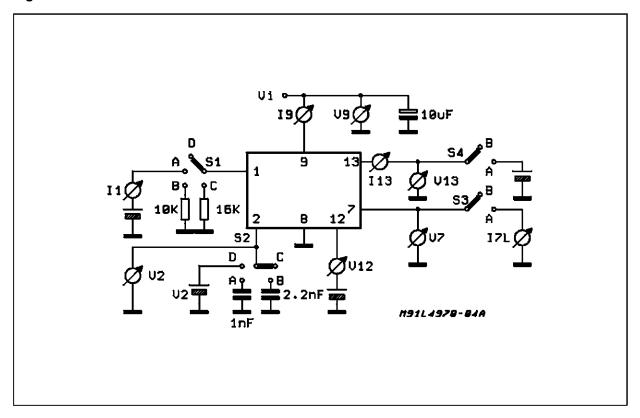

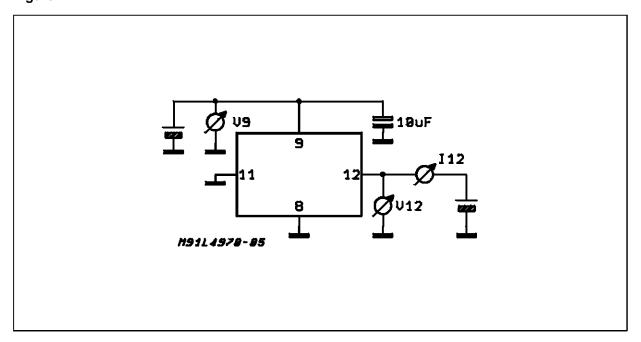

| RESET                                  |                                                                |                                                                                                                 |                            |                            |                            |          |          |

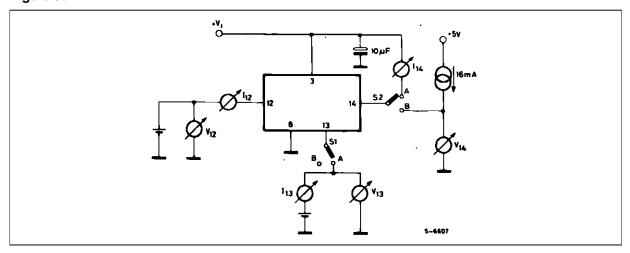

| V <sub>12 R</sub>                      | Rising Threshold Voltage                                       | V <sub>i</sub> = 9V to 46V,                                                                                     | V <sub>ref</sub><br>-150mV | V <sub>ref</sub><br>-100mV | V <sub>ref</sub><br>-50mV  | V        | 6d       |

| V <sub>12</sub> F                      | Falling Threshold Voltage                                      | S1 : B, S2 : B                                                                                                  | 4.75                       | V <sub>ref</sub><br>-150mV | V <sub>ref</sub><br>-100mV | V        | 6d       |

| V <sub>13 D</sub>                      | Delay Thershold Voltage                                        |                                                                                                                 | 4.3                        | 4.5                        | 4.7                        | V        | 6d       |

| V <sub>13</sub> H                      | Delay Threshold Voltage<br>Hysteresis                          | V <sub>12</sub> = 5.3V, S1 : A, S2 : B                                                                          |                            | 100                        |                            | mV       | 6d       |

| V <sub>14</sub> S                      | Output Saturation Voltage                                      | $I_{14} = 16\text{mA}, V_{12} = 4.7\text{V}, S1, S2 : B$                                                        |                            |                            | 0.4                        | V        | 6d       |

| I <sub>12</sub>                        | Input Bias Current                                             | V <sub>12</sub> = 0V to V <sub>ref</sub> , S1 : B, S2 : B                                                       |                            | 1                          | 3                          | μΑ       | 6d       |

| - I <sub>13 so</sub>                   | Delay Source Current<br>Delay Sink Current                     | $V_{13} = 3V, S1 : A, S2 : B$<br>$V_{12} = 5.3V$<br>$V_{12} = 4.7V$                                             | 70<br>10                   | 110                        | 140                        | μA<br>mA | 6d       |

| I <sub>14</sub>                        | Output Leakage Current                                         | $V_i = 46V, V_{12} = 5.3V, S1 : B, S2 : A$                                                                      |                            |                            | 100                        | μΑ       | 6d       |

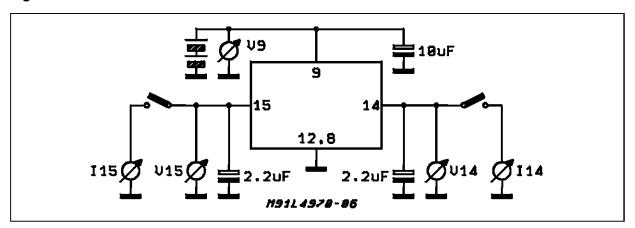

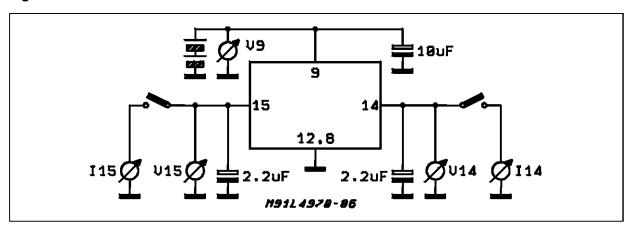

| CROWBA                                 | R                                                              |                                                                                                                 |                            |                            |                            |          |          |

| V <sub>1</sub>                         | Input Threshold Voltage                                        | S1 : B                                                                                                          | 5.5                        | 6                          | 6.4                        | V        | 6b       |

| V <sub>15</sub>                        | Output Saturation Voltage                                      | $V_i = 9V \text{ to } 46V, \ V_i = 5.4V, \ I_{15} = 5mA, \ S1: A$                                               |                            | 0.2                        | 0.4                        | V        | 6b       |

| l <sub>1</sub>                         | Input Bias Current                                             | V <sub>1</sub> = 6V, S1 : B                                                                                     |                            |                            | 10                         | μΑ       | 6b       |

| - I <sub>15</sub>                      | Output Source Current                                          | $V_i = 9V \text{ to } 46V, V_1 = 6.5V, V_{15} = 2V, S1 : B$                                                     | 70                         | 100                        |                            | mA       | 6b       |

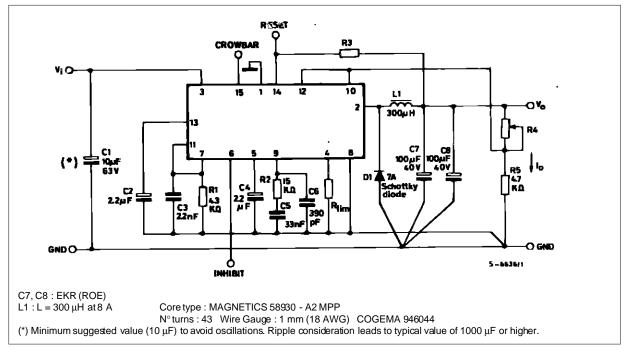

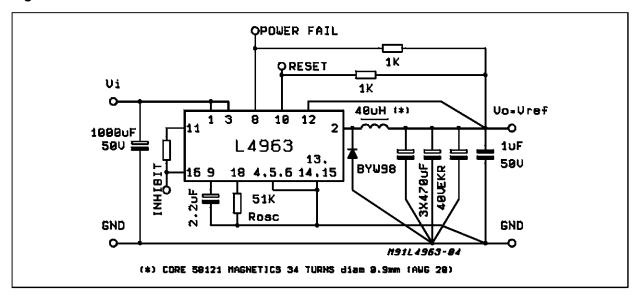

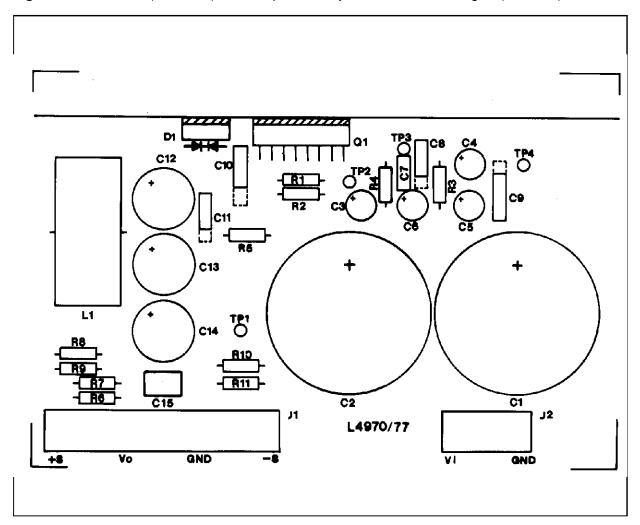

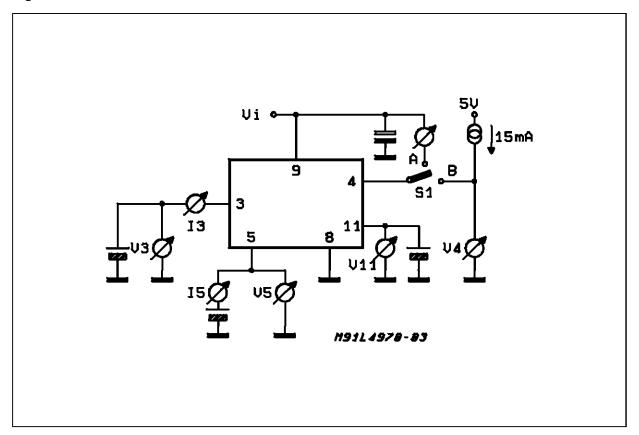

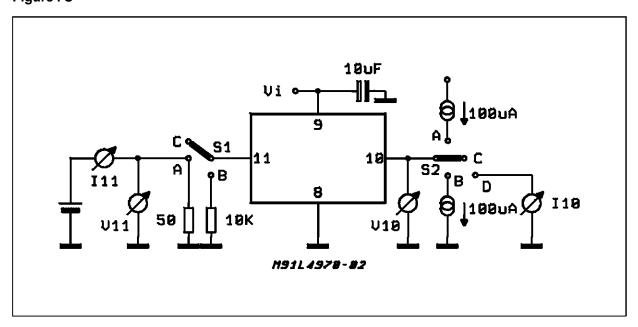

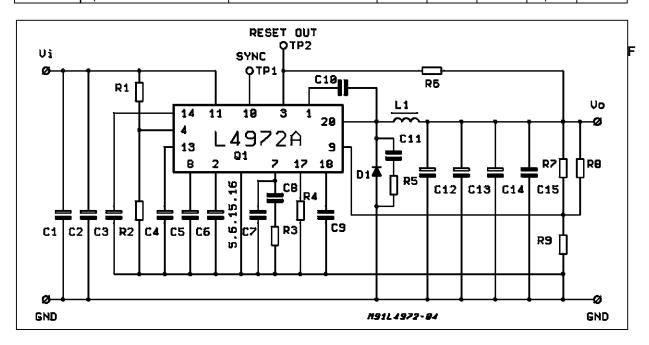

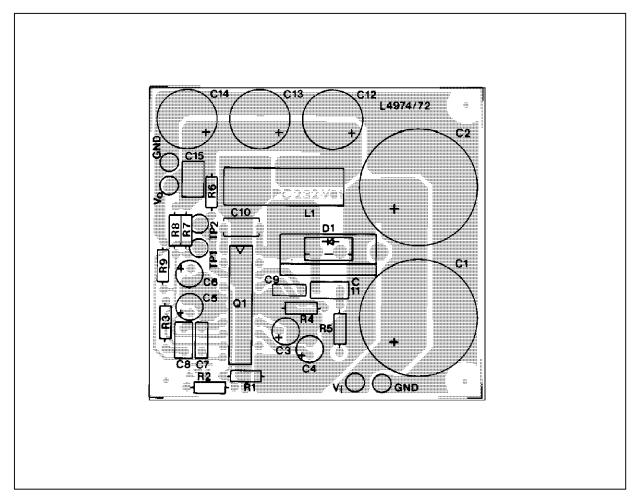

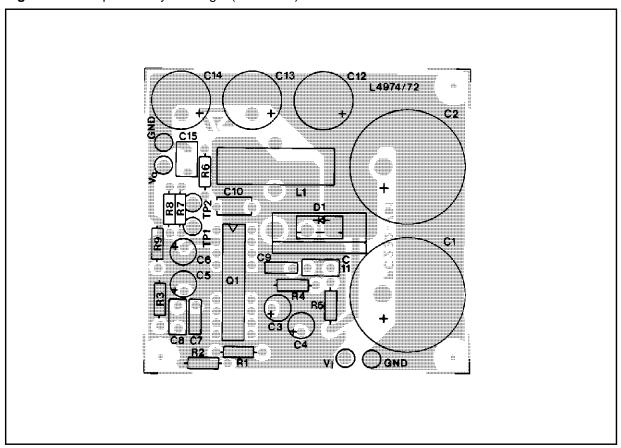

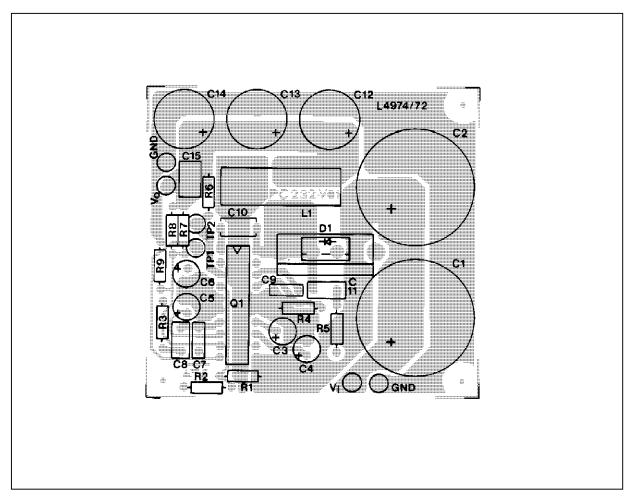

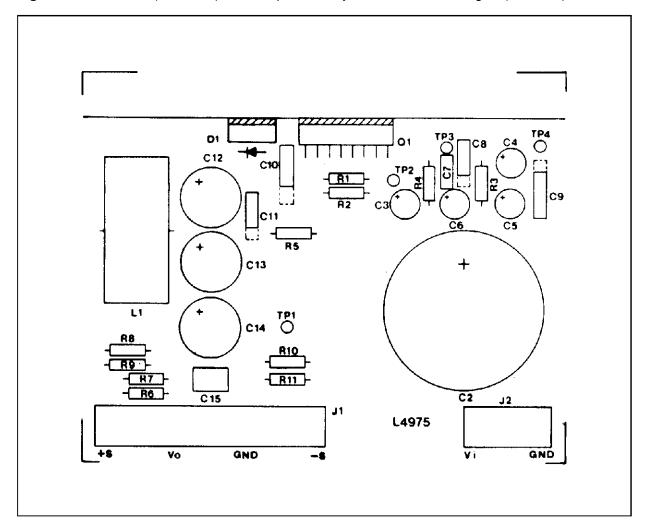

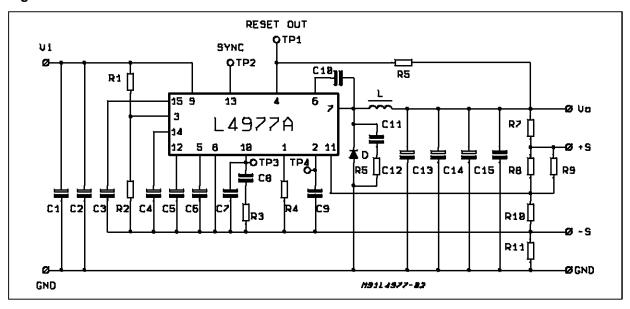

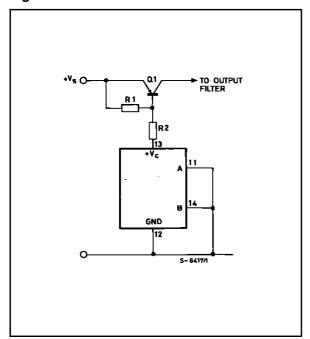

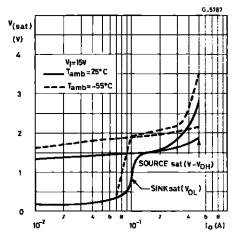

Figure 4: Dynamic Test Circuit

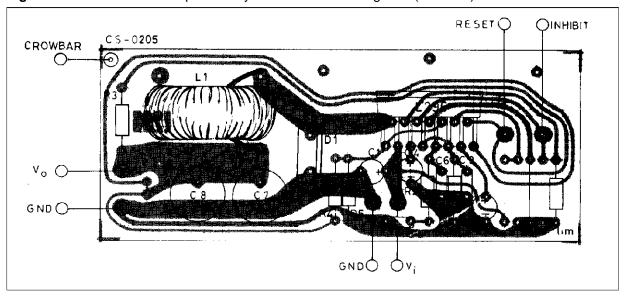

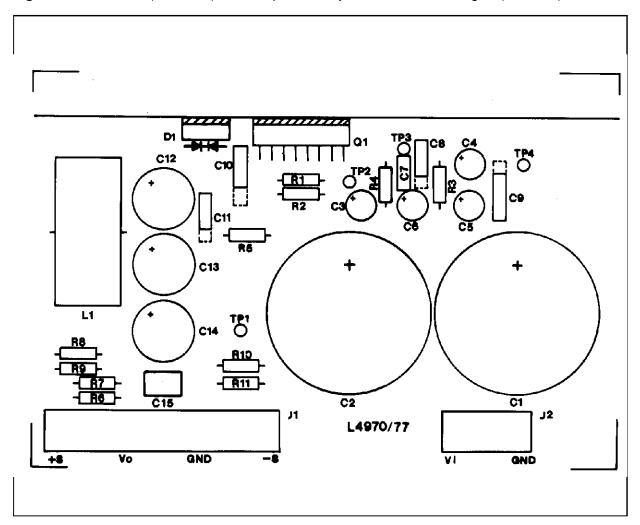

Figure 5: PC. Board and Component Layout of the Circuit of Figure 4 (1:1 scale)

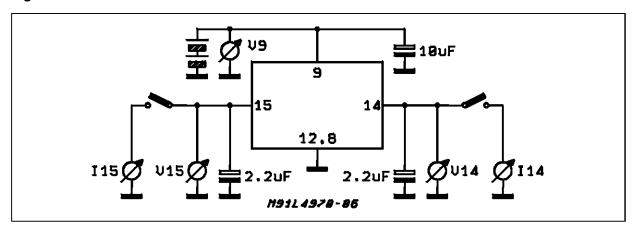

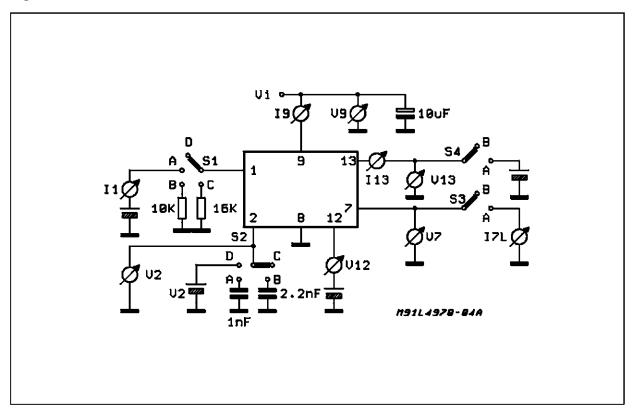

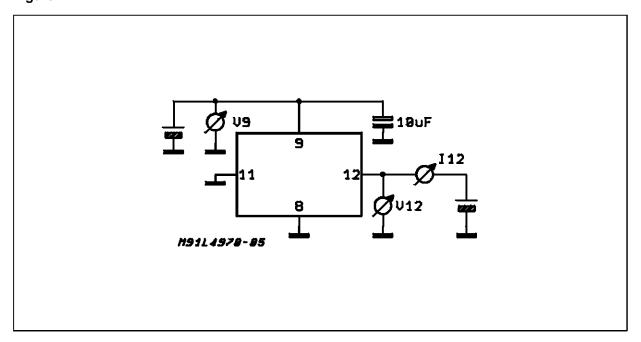

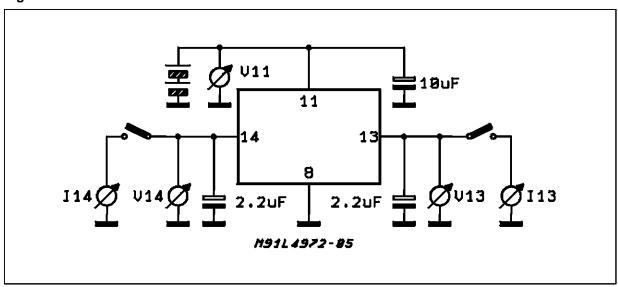

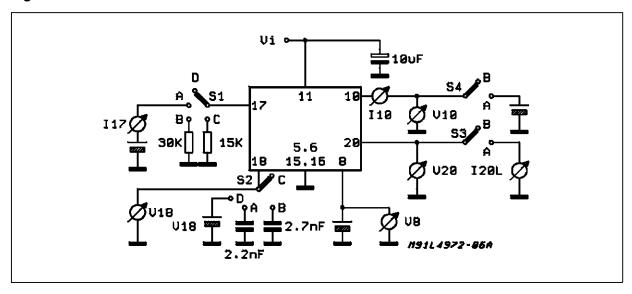

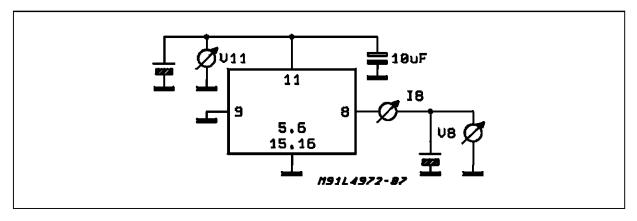

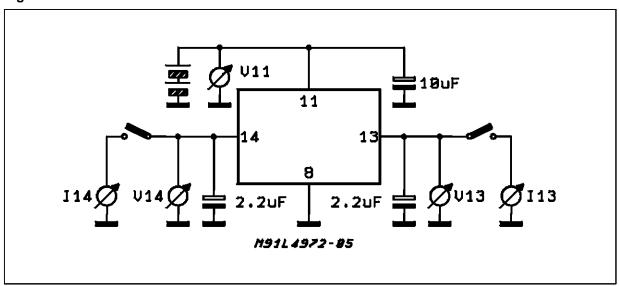

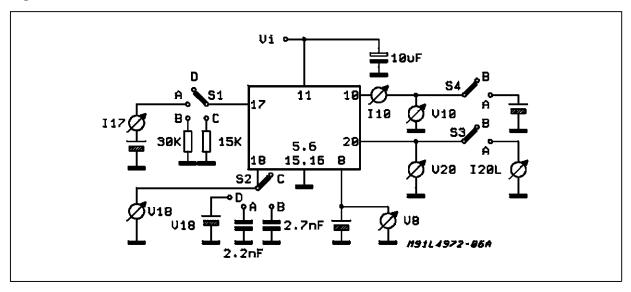

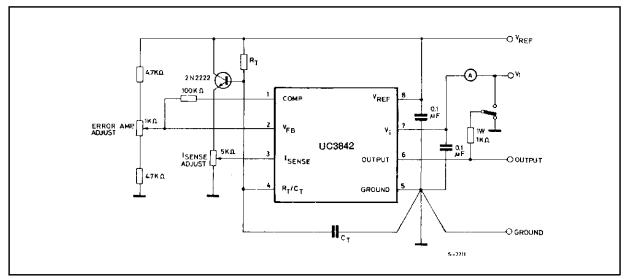

Figure 6 : DC Test Circuits.

Figure 6a.

Figure 6b.

Figure 6c.

Figure 6d.

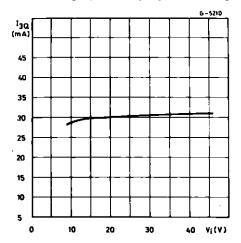

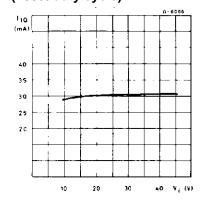

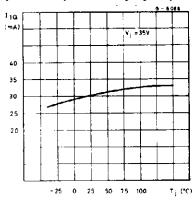

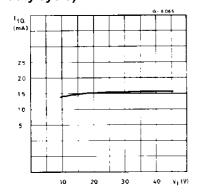

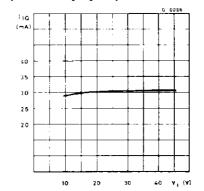

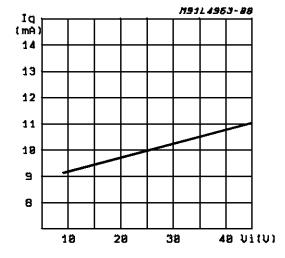

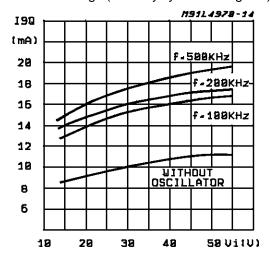

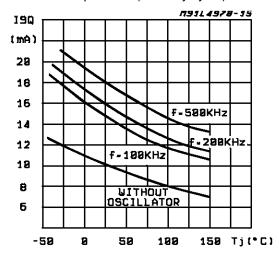

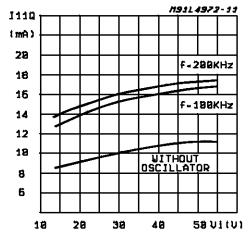

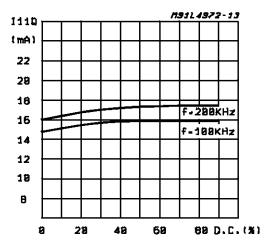

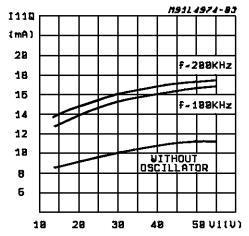

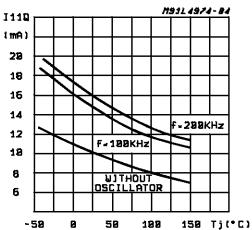

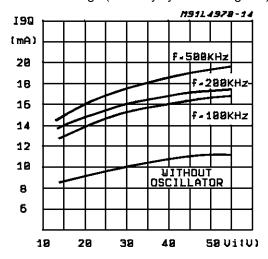

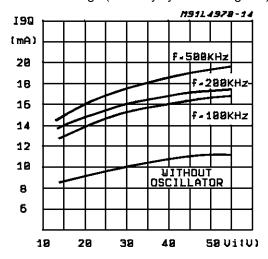

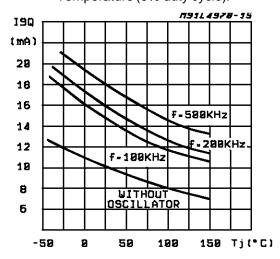

Figure 7: Quienscent Drain Current vs. Supply Voltage (0 % Duty Cycle - see fig. 6a).

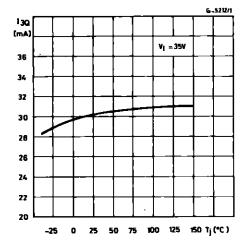

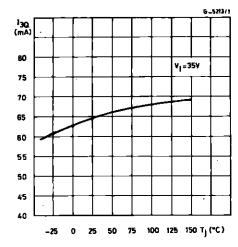

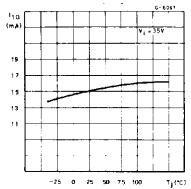

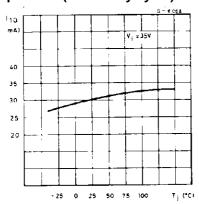

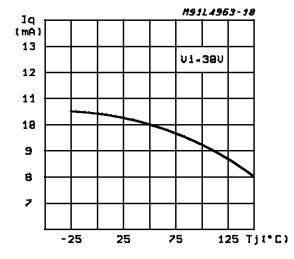

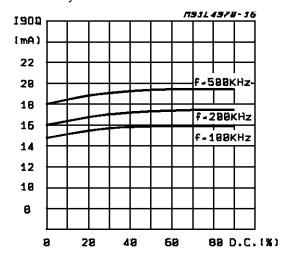

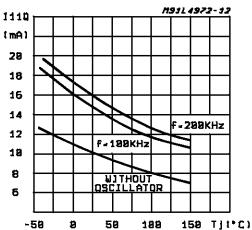

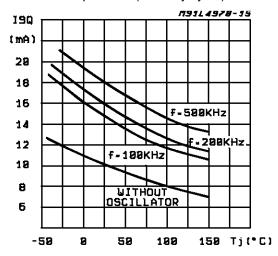

Figure 9: Quiescent Drain Current vs. Junction Temperature (0 % Duty Cycle see fig. 6a).

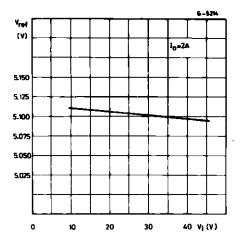

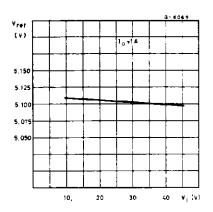

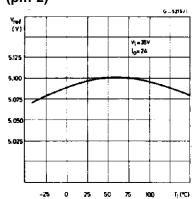

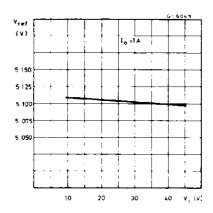

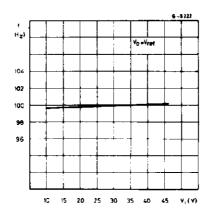

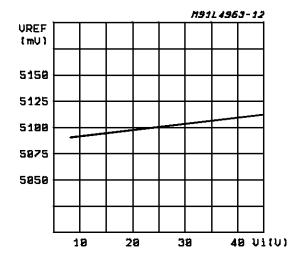

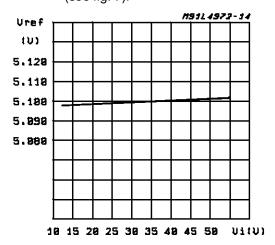

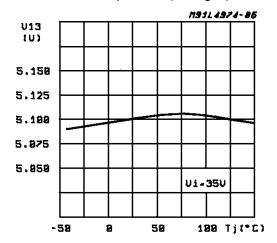

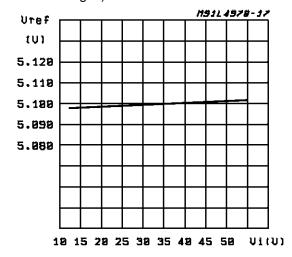

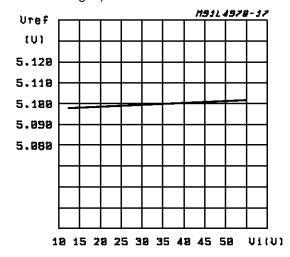

Figure 11: Reference Voltage (pin 10) vs. V<sub>I</sub> (see fig. 4).

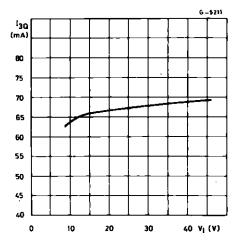

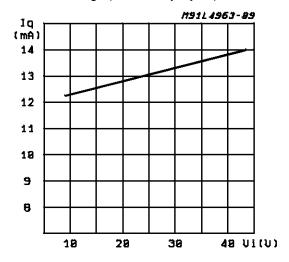

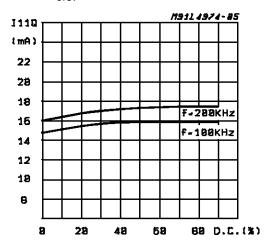

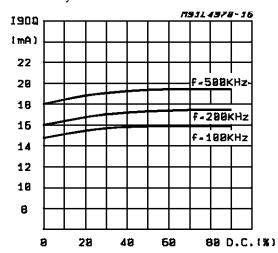

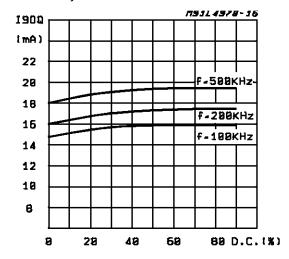

Figure 8: Quienscent Drain Current vs. Supply Voltage (100 % Duty Cycle see fig. 6a).

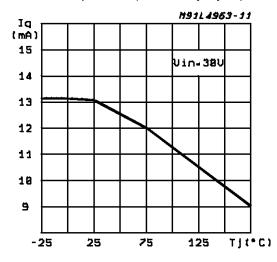

Figure 10: Quiescent Drain Current vs. Junction Temperature (100 % Duty Cycle see fig. 6a).

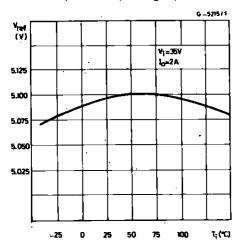

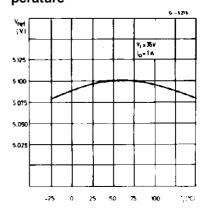

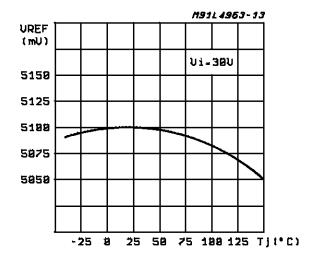

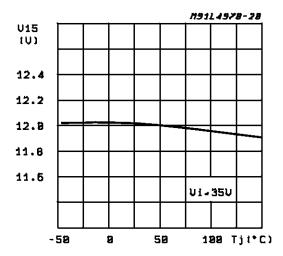

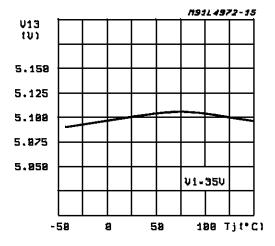

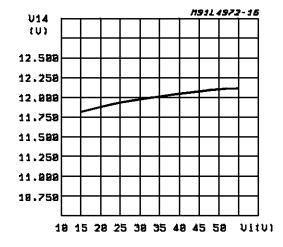

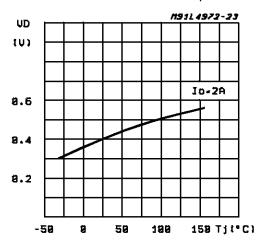

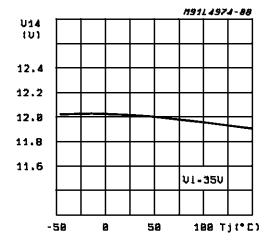

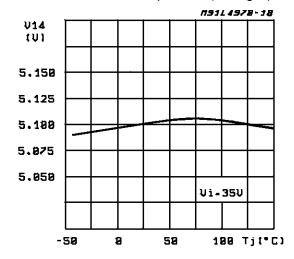

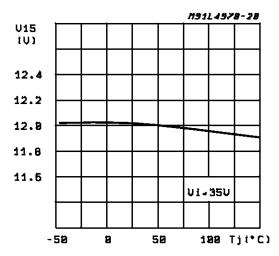

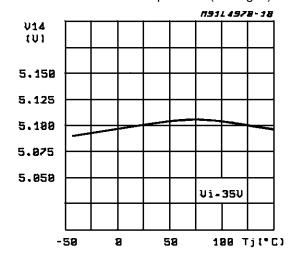

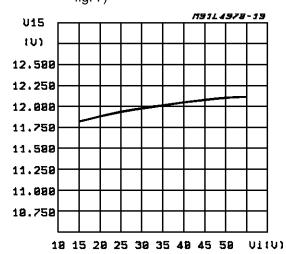

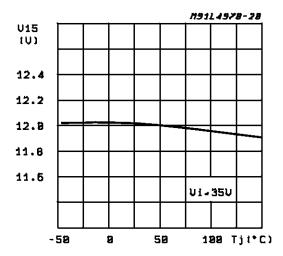

**Figure 12 :** Reference Voltage (pin 10) vs. Junction Temperature (see fig. 4).

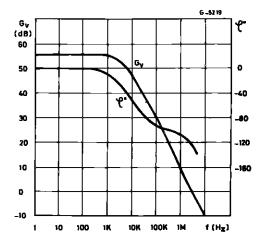

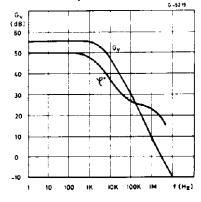

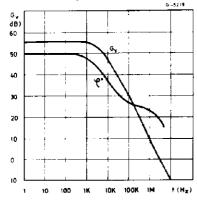

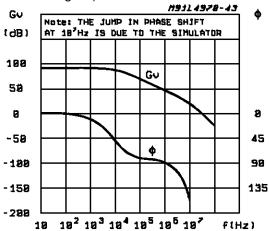

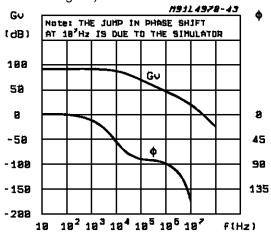

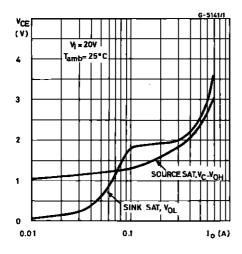

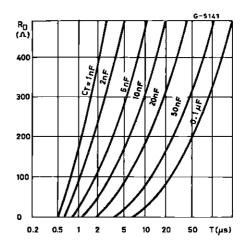

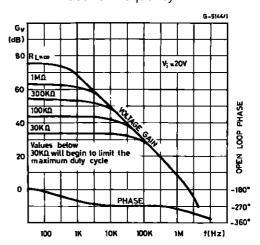

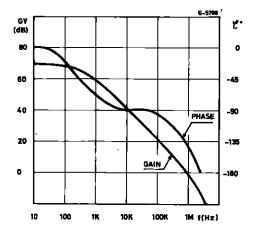

Figure 13: Open Loop Frequency and Phase Response of Error Amplifier (see fig. 6c).

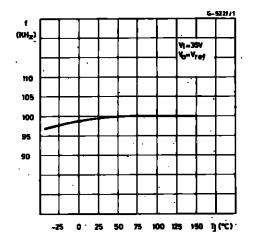

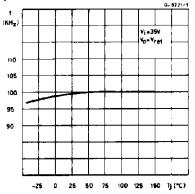

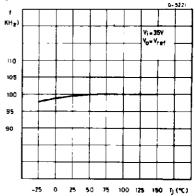

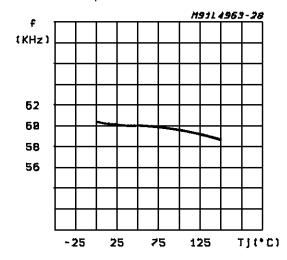

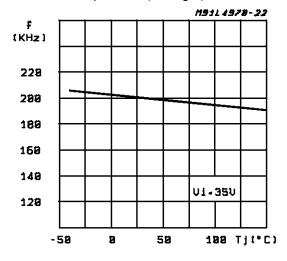

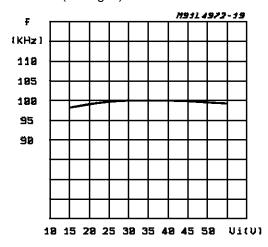

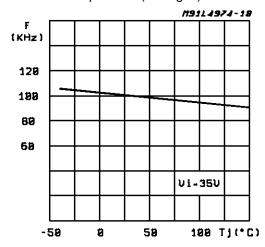

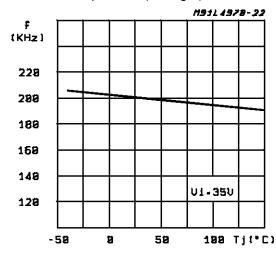

**Figure 15 :** Switching Frequency vs. Junction Temperature (see fig. 4).

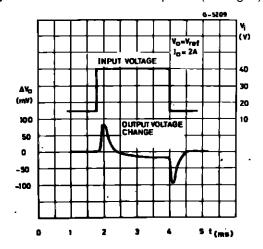

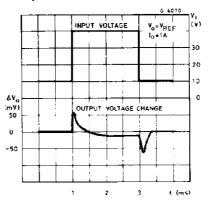

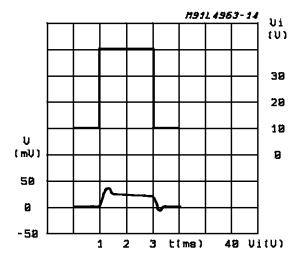

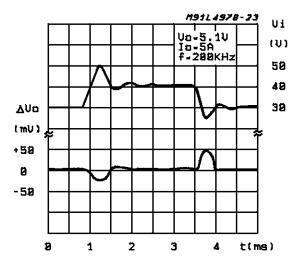

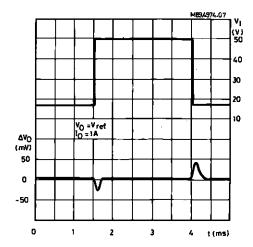

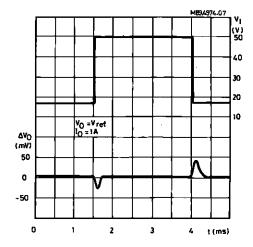

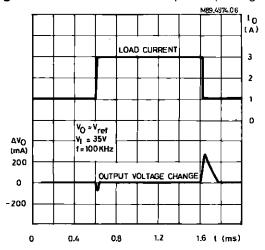

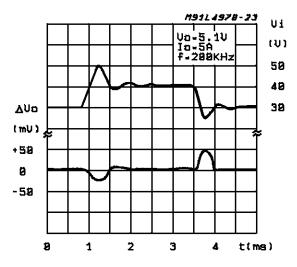

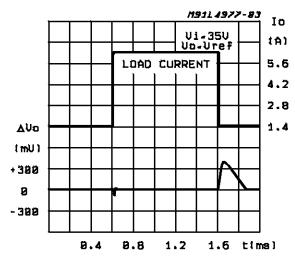

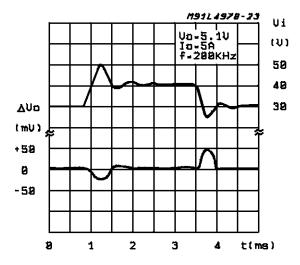

Figure 17: Line Transient Response (see fig. 4).

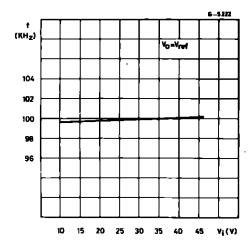

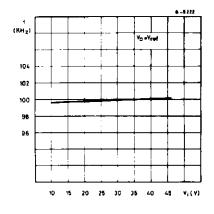

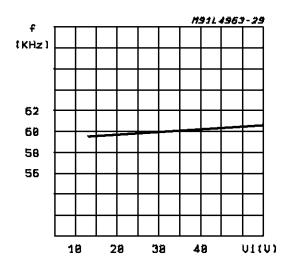

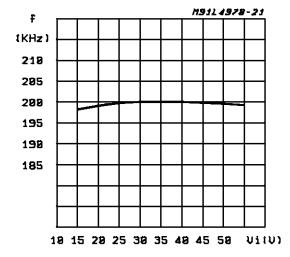

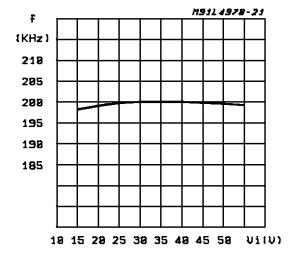

**Figure 14 :** Switching Frequency vs. Input Voltage (see fig. 4).

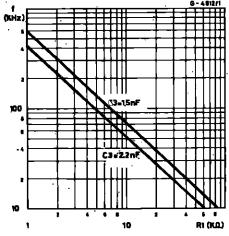

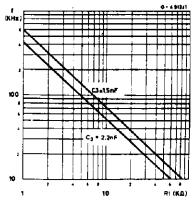

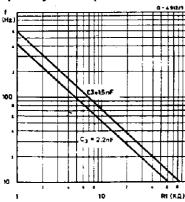

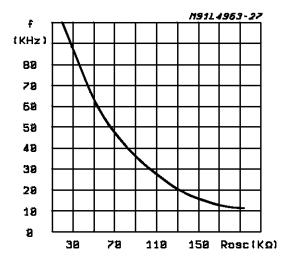

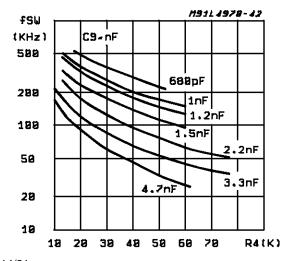

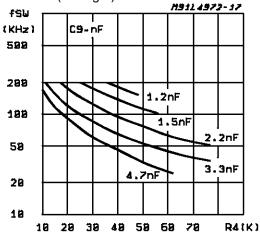

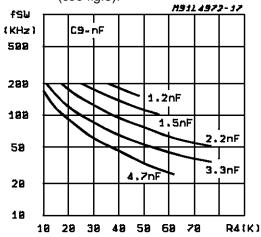

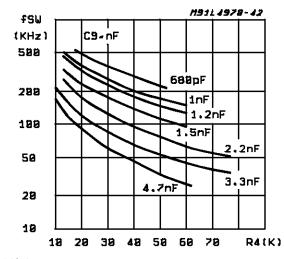

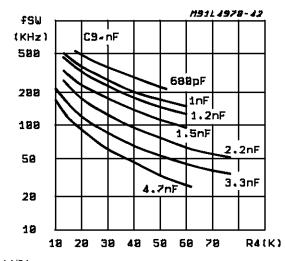

**Figure 16 :** Switching Frequency vs. R1 (see fig. 4).

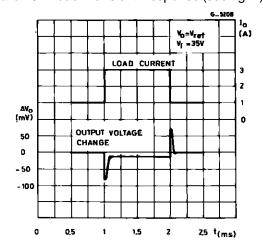

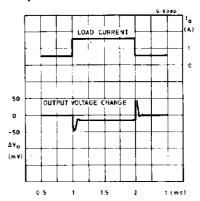

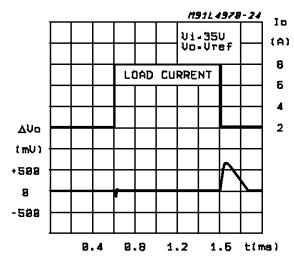

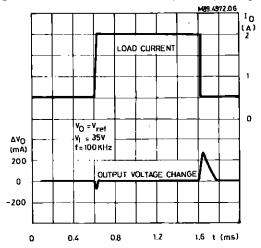

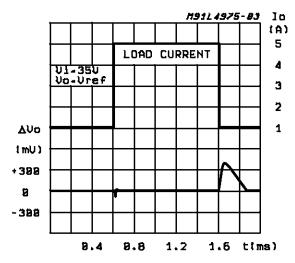

Figure 18: Load Transient Response (see fig. 4).

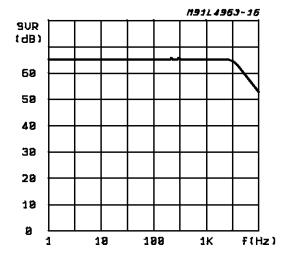

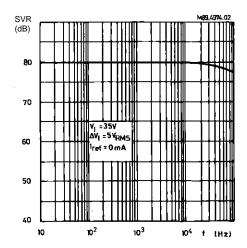

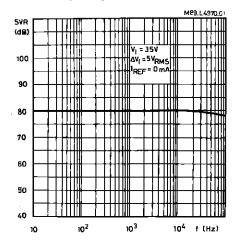

Figure 19: Supply Voltage Ripple Rejection vs. Frequency (see fig. 4).

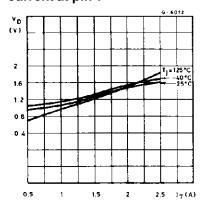

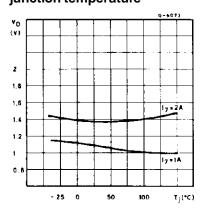

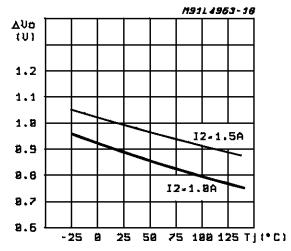

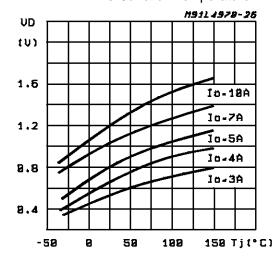

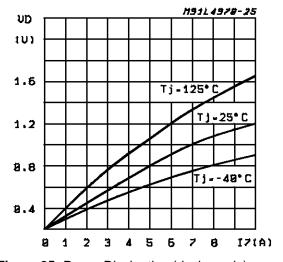

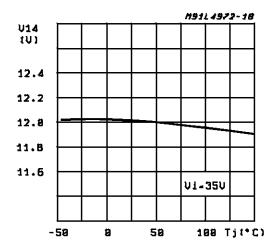

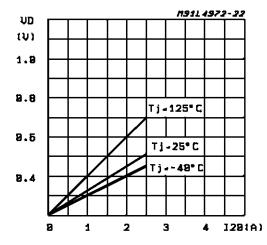

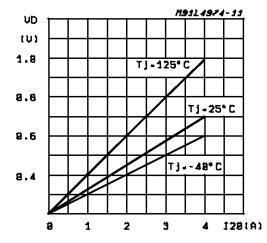

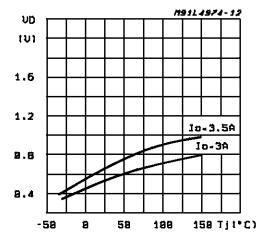

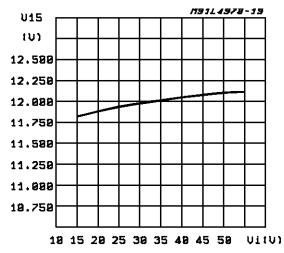

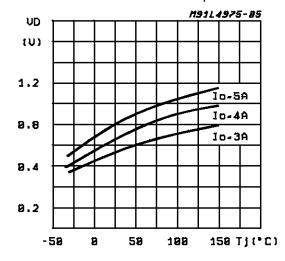

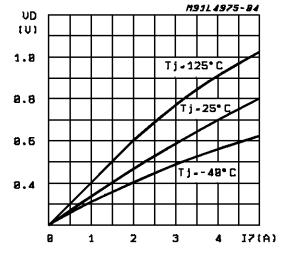

**Figure 21 :** Dropout Voltage Between Pin 3 and Pin 2 vs. Junction Temperature.

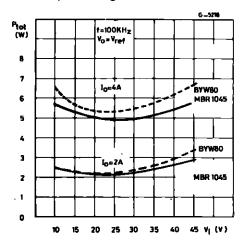

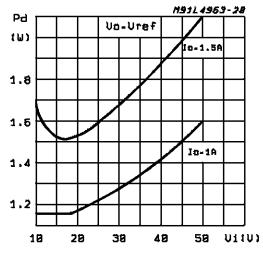

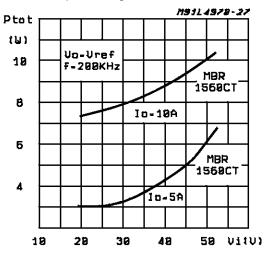

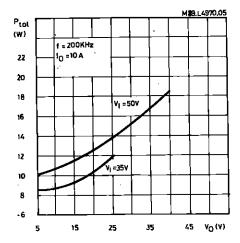

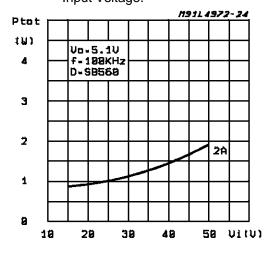

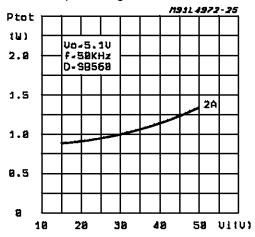

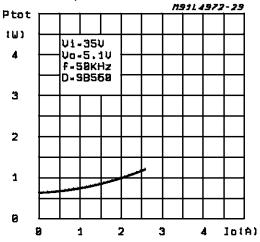

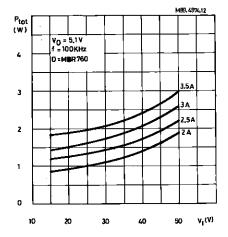

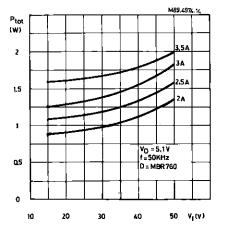

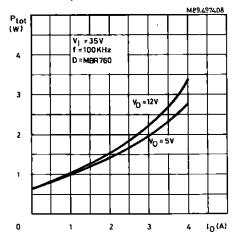

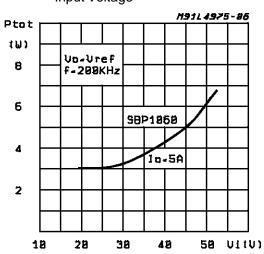

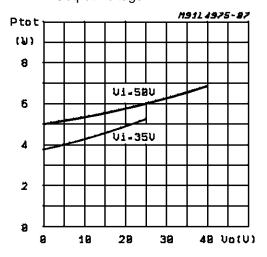

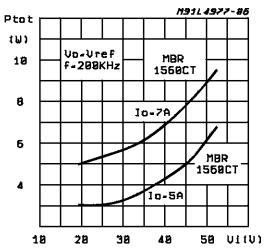

**Figure 23 :** Power Dissipation (device only) vs. Input Voltage.

**Figure 20 :** Dropout Voltage Between Pin 3 and Pin 2 vs. Current at Pin 2.

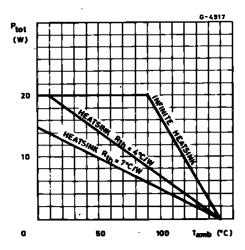

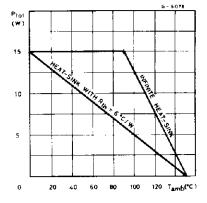

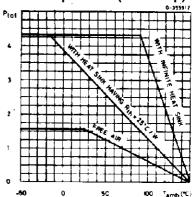

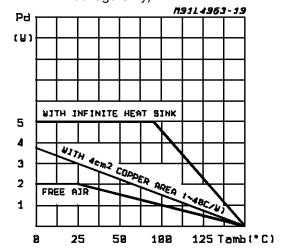

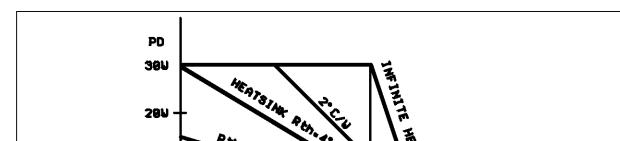

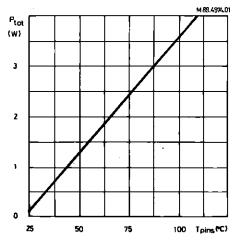

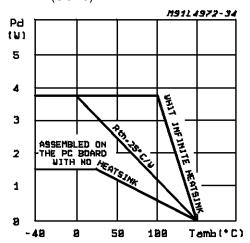

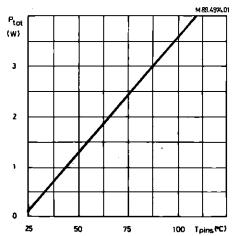

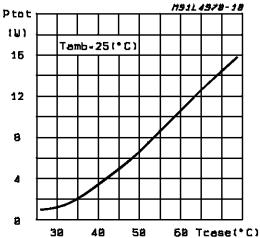

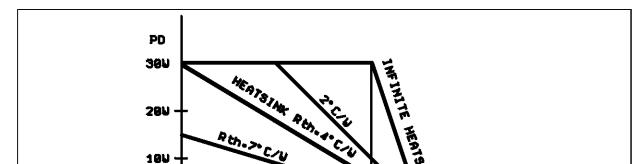

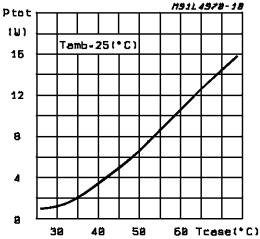

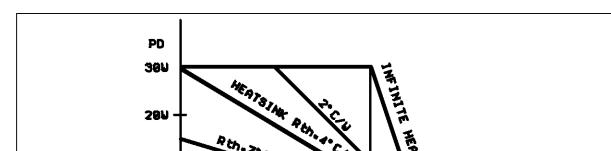

Figure 22: Power Dissipation Derating Curve.

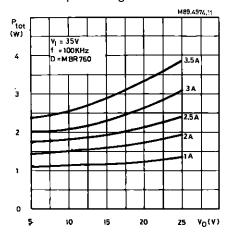

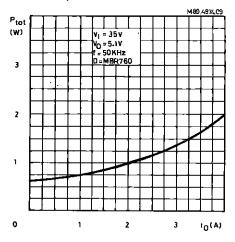

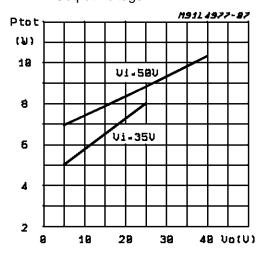

**Figure 24 :** Power Dissipation (device only) vs. Input voltage.

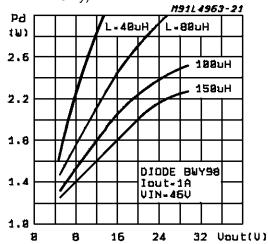

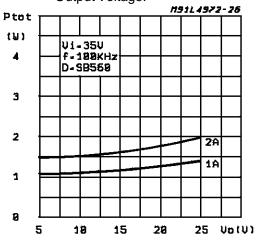

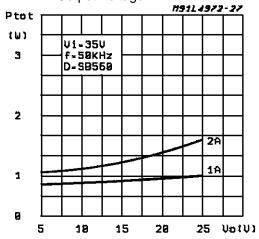

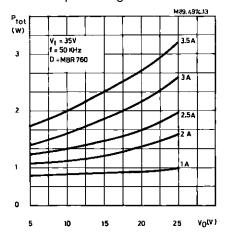

Figure 25: Power Dissipation (device only) vs. Output Voltage (see fig. 4).

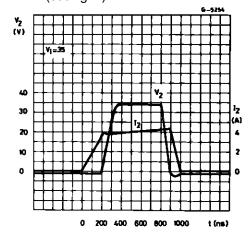

Figure 27: Voltage and Current Waveforms at Pin 2 (see fig. 4).

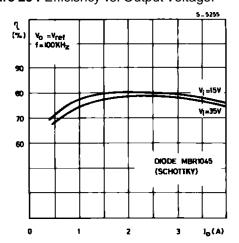

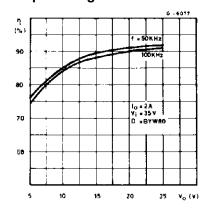

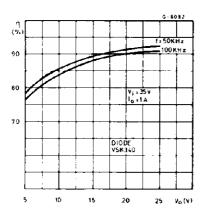

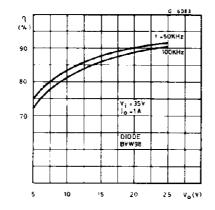

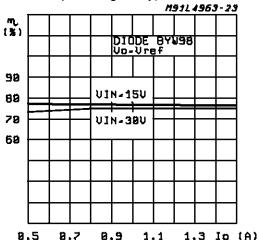

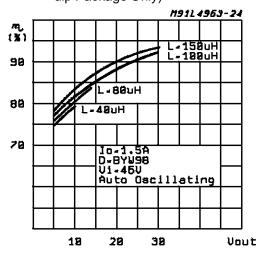

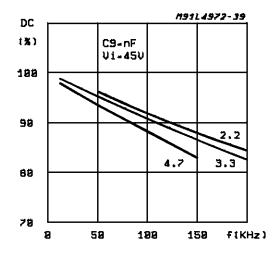

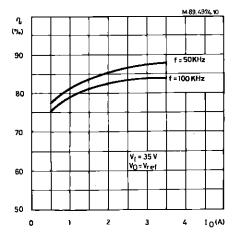

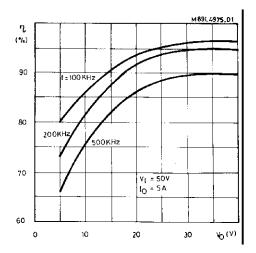

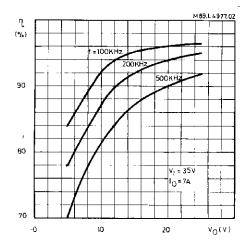

Figure 29: Efficiency vs. Output Voltage.

**Figure 26 :** Power Dissipation (device only) vs. Output Voltage (see fig. 4).

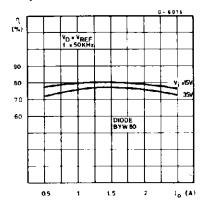

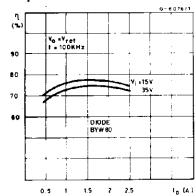

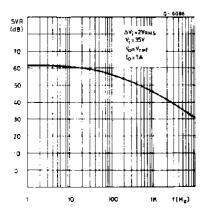

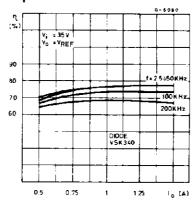

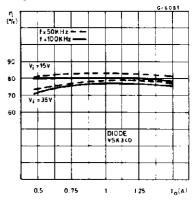

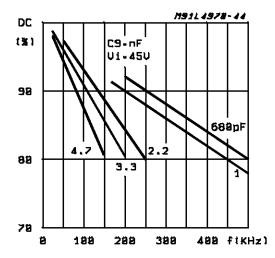

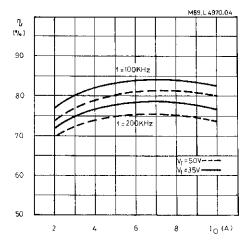

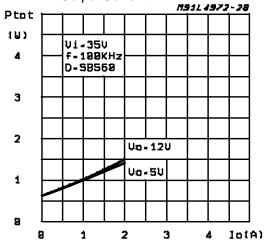

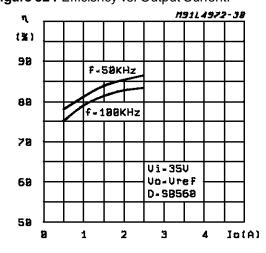

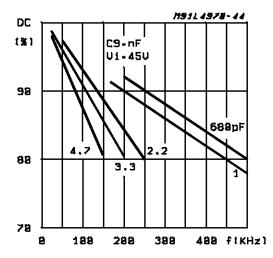

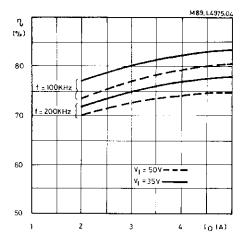

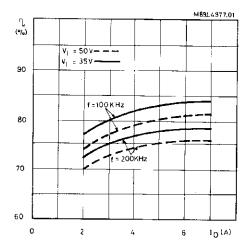

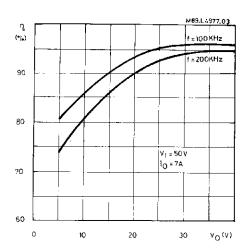

Figure 28 : Efficiency vs. Output Current.

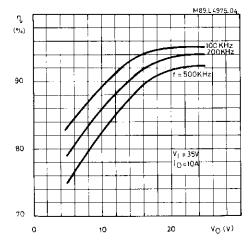

Figure 30: Efficiency vs. Output Voltage.

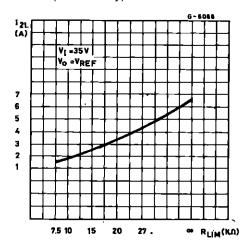

**Figure 31 :** Current Limiting Threshold vs. R<sub>pin 4</sub> (L296P only).

**Figure 33 :** Current Limiting Threshold vs. Supply Voltage.

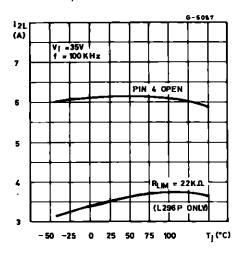

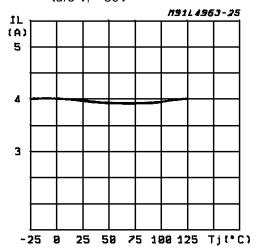

**Figure 32 :** Current Limiting Threshold vs. Junction Temperature.

#### **APPLICATION INFORMATION**

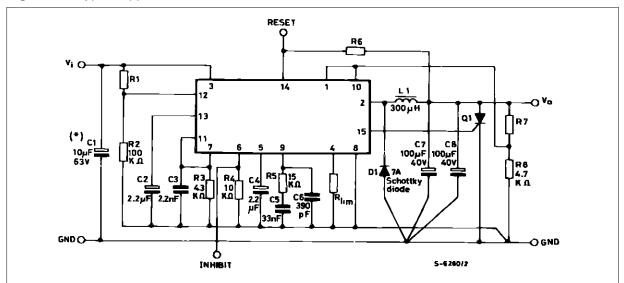

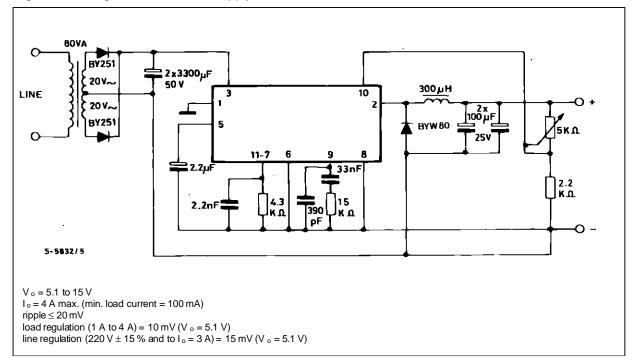

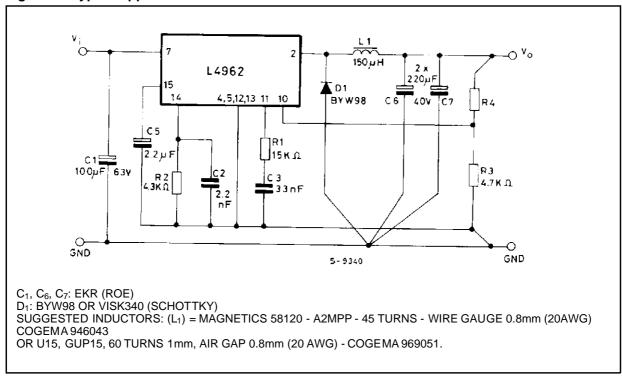

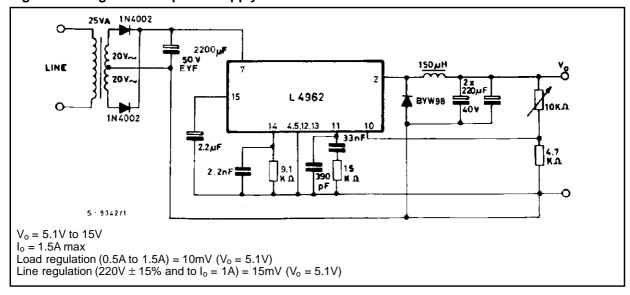

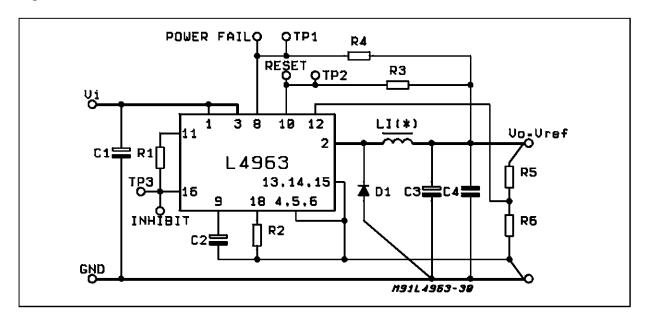

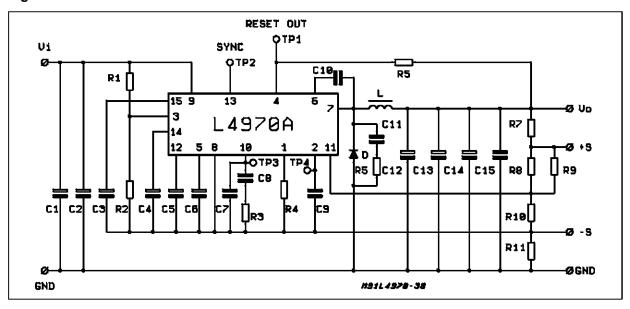

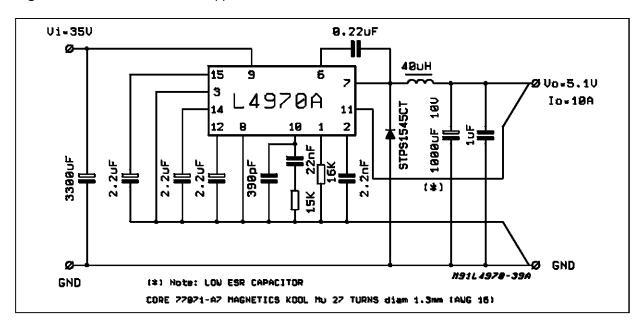

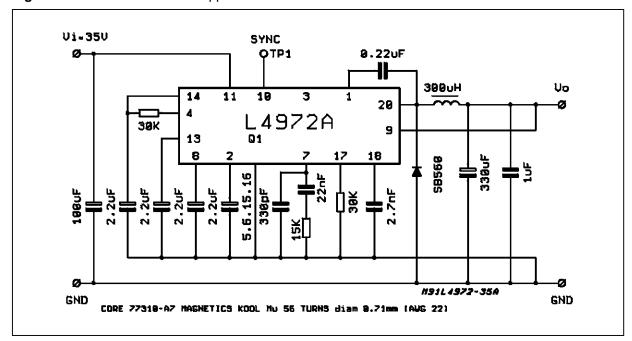

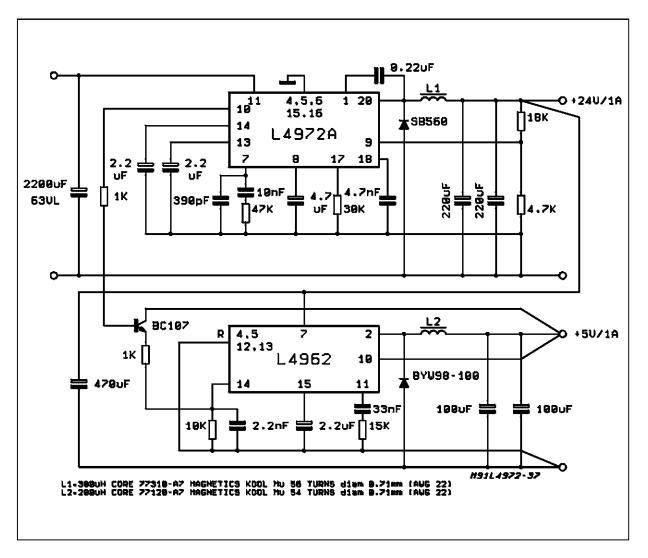

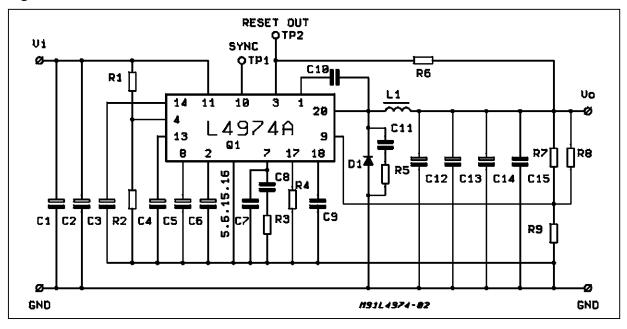

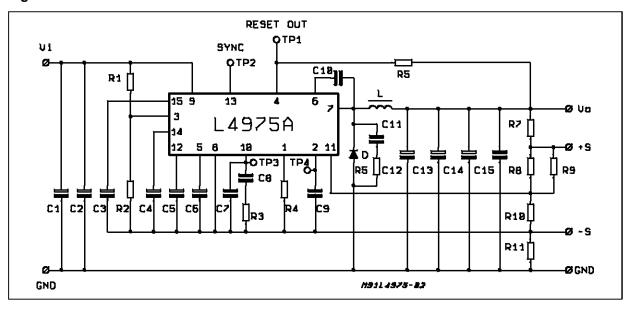

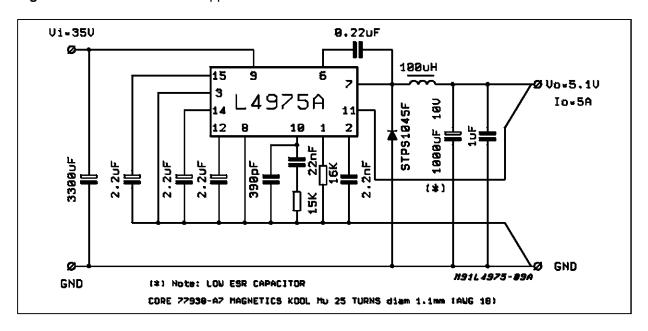

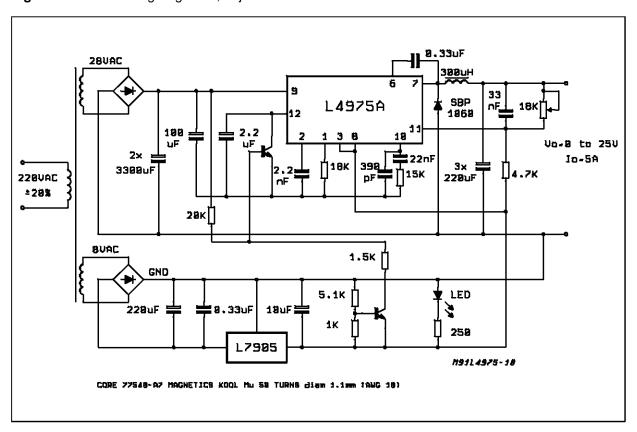

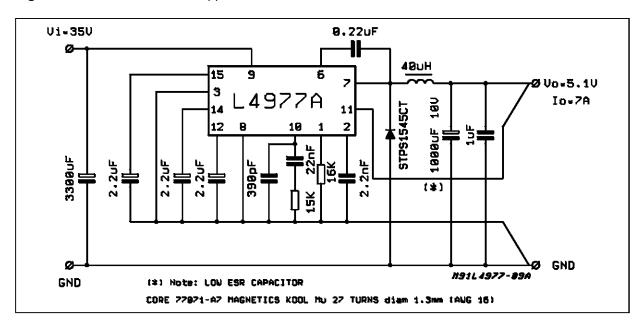

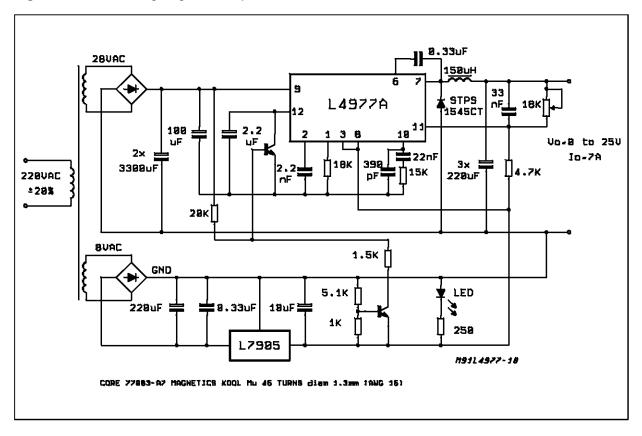

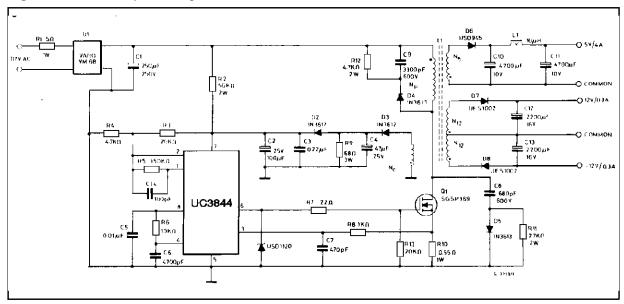

Figure 34: Typical Application Circuit.

(\*) Minimum value (10  $\mu$ F) to avoid oscillations ; ripple consideration leads to typical value of 1000  $\mu$ F or higher L1 : 58930 - MPP COGEMA 946044 ; GUP 20 COGEMA 946045

# **SUGGESTED INDUCTOR** (L1)

| Core Type                                         | No Turns | Wire Gauge | Air Gap |

|---------------------------------------------------|----------|------------|---------|

| Magnetics 58930 – A2MPP                           | 43       | 1.0 mm     | _       |

| Thomson GUP 20 x 16 x 7                           | 65       | 0.8 mm     | 1 mm    |

| Siemens EC 35/17/10 (B6633& - G0500 - X127)       | 40       | 2 x 0.8 mm | _       |

| VOGT 250 μH Toroidal Coil, Part Number 5730501800 |          |            |         |

| Resistor Values for Standard Output Voltages |                                      |                                    |  |  |

|----------------------------------------------|--------------------------------------|------------------------------------|--|--|

| V <sub>0</sub> R8 R7                         |                                      |                                    |  |  |

| 12 V<br>15 V<br>18 V<br>24 V                 | 4.7 ΚΩ<br>4.7 ΚΩ<br>4.7 ΚΩ<br>4.7 ΚΩ | 6.2 ΚΩ<br>9.1 ΚΩ<br>12 ΚΩ<br>18 ΚΩ |  |  |

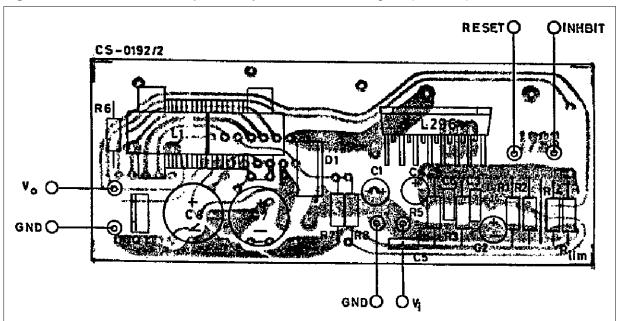

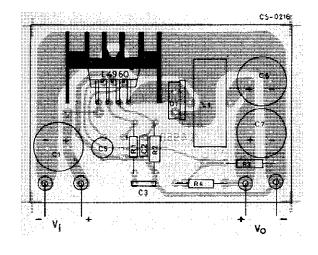

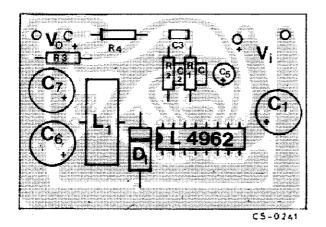

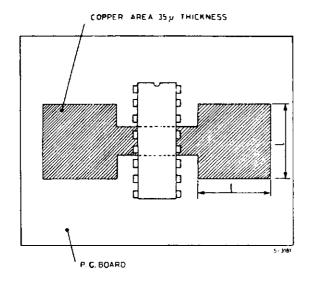

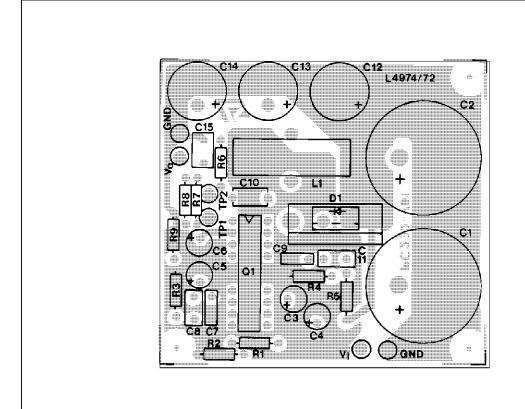

Figure 35: P.C. Board and Component Layout of the Circuit of fig. 34 (1:1 scale)

# SELECTION OF COMPONENT VALUES (see fig. 34)

| Component        | Recommended Purpose |                                           | Allowe              | d Rage   | Notes                                                                                                                             |  |

|------------------|---------------------|-------------------------------------------|---------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------|--|

| Component        | Value               | ruipose                                   | Min.                | Max.     | Notes                                                                                                                             |  |

| R1<br>R2         | _<br>100 kΩ         | Set Input Voltage<br>Threshold for Reset. | _                   | 220kΩ    | $R1/R2 \frac{V_{i  min}}{5} - 1$                                                                                                  |  |

|                  |                     |                                           |                     |          | If output voltage is sensed R1 and R2 may be limited and pin 12 connected to pin 10.                                              |  |

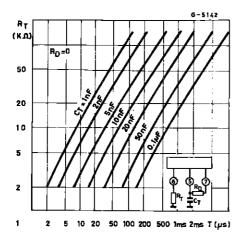

| R3               | 4.3 kΩ              | Sets Switching Frequency                  | 1 kΩ                | 100kΩ    |                                                                                                                                   |  |

| R4               | 10 kΩ               | Pull-down Resistor                        |                     | 22kΩ     | May be omitted and pin 6 grounded if inhibit not used.                                                                            |  |

| R5               | 15 kΩ               | Frequency Compensation                    | 10kΩ                |          |                                                                                                                                   |  |

| R6               |                     | Collector Load For Reset<br>Output        | $\frac{V_0}{0.05A}$ |          | Omitted if reset function not used.                                                                                               |  |

| R7<br>R8         | _<br>4.7 kΩ         | Divider to Set Output<br>Voltage          | _                   | _<br>1kΩ | $R7/R8 = \frac{V_0 - V_{REF}}{V_{REF}} -$                                                                                         |  |

| R <sub>iim</sub> | _                   | Sets Current Limit Level                  | 7.5kΩ               |          | If R <sub>iim</sub> is omitted and pin 4 left open the current limit is internally fixed.                                         |  |

| C1               | 10 μF               | Stability                                 | 2.2μF               |          |                                                                                                                                   |  |

| C2               | 2.2 μF              | Sets Reset Delay                          | _                   | _        | Omitted if reset function not used.                                                                                               |  |

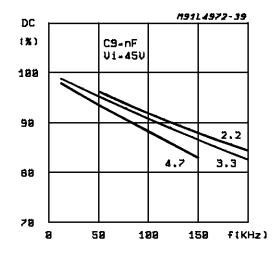

| C3               | 2.2 nF              | Sets Switching Frequency                  | 1 nF                | 3.3nF    |                                                                                                                                   |  |

| C4               | 2.2 μF              | Soft Start                                | 1 μF                | _        | Also determines average short circuit current.                                                                                    |  |

| C5               | 33 nF               | Frequency Compensation                    |                     |          |                                                                                                                                   |  |

| C6               | 390 pF              | High Frequency<br>Compensation            | _                   | _        | Not required for 5 V operation.                                                                                                   |  |

| C7, C8<br>L1     | 100 μF<br>300 μH    | Output Filter                             | _<br>100μH          | _        |                                                                                                                                   |  |

| Q1               |                     | Crowbar Protection                        |                     |          | The SCR must be able to withstand the peak discharge current of the output capacitor and the short circuit current of the device. |  |

| D1               |                     | Recirculation Diode                       |                     |          | 7A Schottky or 35 ns t <sub>rr</sub> Diode.                                                                                       |  |

Figure 36: A Minimal 5.1 V Fixed Regulator. Very Few Components are Required.

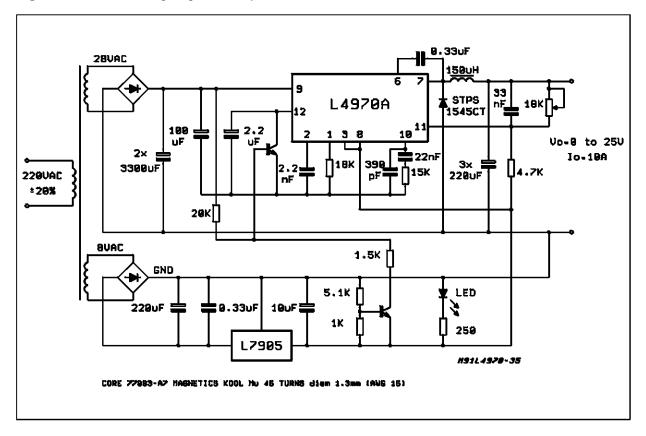

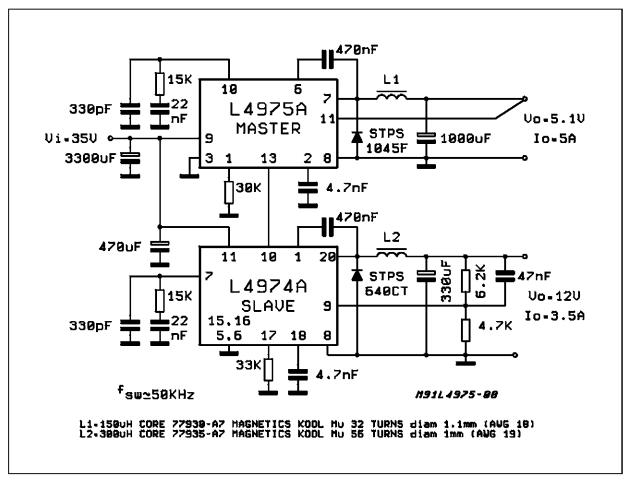

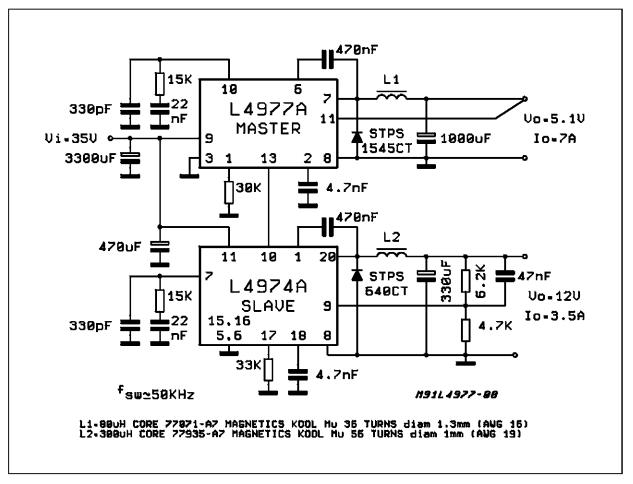

Figure 37: 12 V/10 A Power Supply.

Figure 38: Programmable Power Supply.

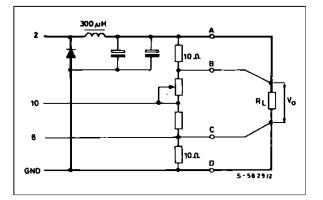

Figure 39: Preregulator for Distributed Supplies.

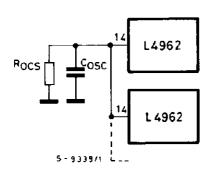

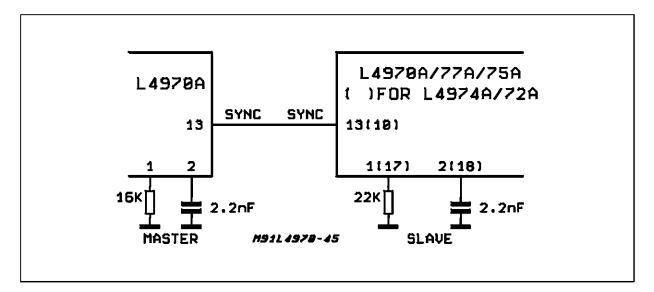

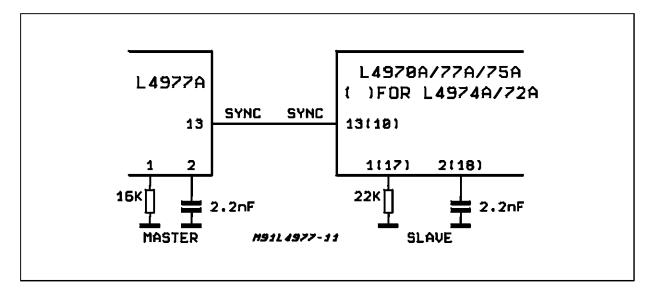

Figure 40: In Multiple Supplies Several L296s can be Synchronized As Shown.

Figure 41 : Voltage Sensing for Remote Load.

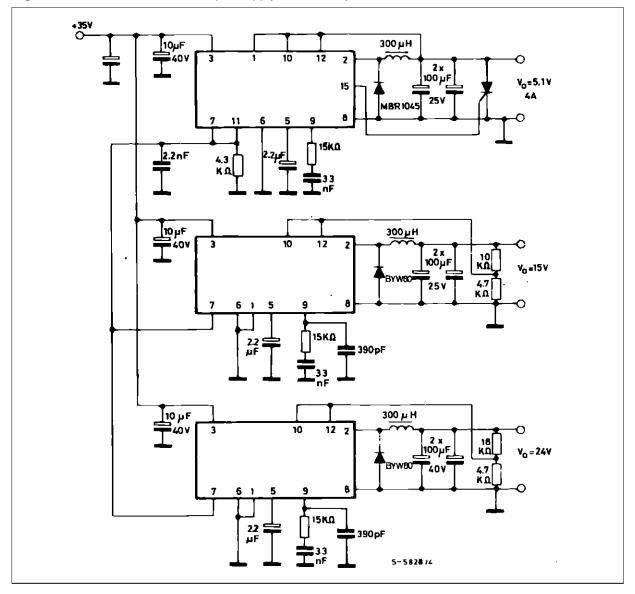

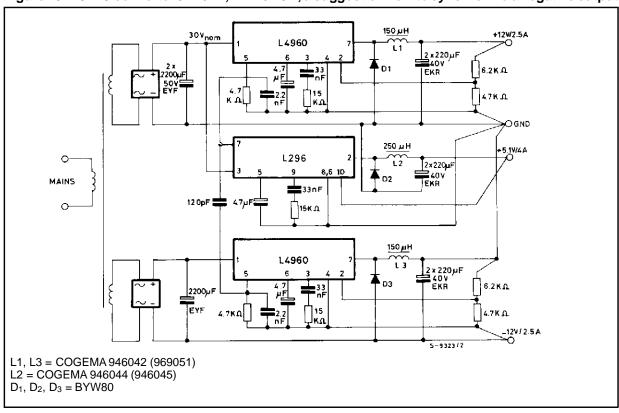

Figure 42: A 5.1 V/15 V/24 V Multiple Supply. Note the Synchronization of the Three L296s.

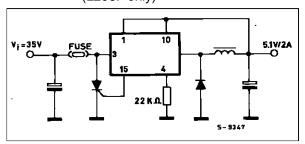

Figure 43: 5.1V/2A Power Supply using External Limiting Current Resistor and Crowbar Protection on the Supply Voltage (L296P only)

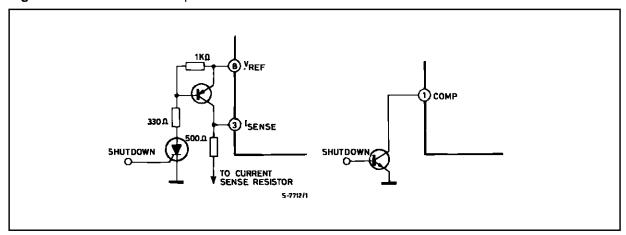

#### SOFT-START AND REPETITIVE POWER-ON

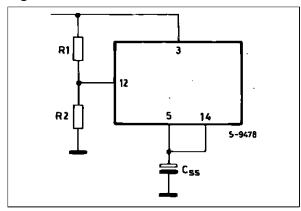

When the device is repetitively powered-on, the softstart capacitor, C<sub>SS</sub>, must be discharged rapidly to ensure that each start is "soft". This can be achieved economically using the reset circuit, as shown in Figure 44.

In this circuit the divider R1, R2 connected to pin 12 determines the minimum supply voltage, below which the open collector transistor at the pin 14 output discharges  $C_{\rm SS}$ .

Figure 44

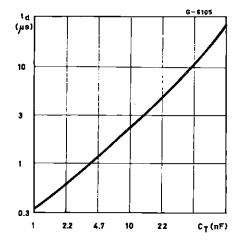

The approximate discharge times obtained with this circuit are:

| CSS (μF) | tDIS (μs) |

|----------|-----------|

| 2.2      | 200       |

| 4.7      | 300       |

| 10       | 600       |

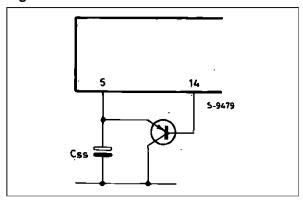

If these times are still too long, an external PNP tran-

sistor may be added, as shown in Figure 45; with this circuit discharge times of a few microseconds may be obtained.

Figure 45

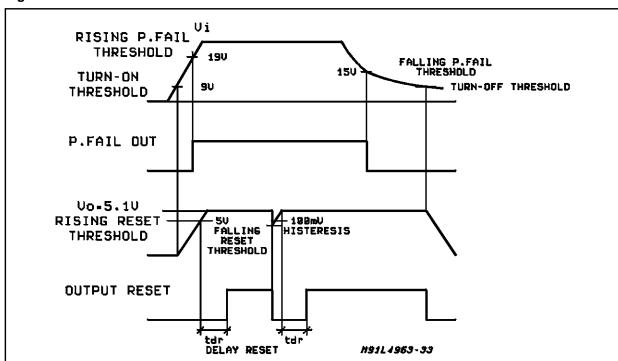

# HOW TO OBTAIN BOTH RESET AND POWER FAIL

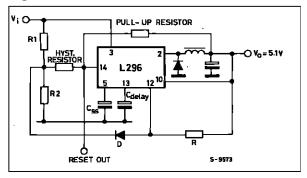

Figure 46 illustrates how it is possible to obtain at the same time both the power fail and reset functions simply by adding one diode (D) and one resistor (R). In this case the Reset delay time (pin 13) can only start when the output voltage is  $V_O \ge V_{REF}$  - 100mV and the voltage accross R2 is higher than 4.5V.

With the hysteresis resistor it is possible to fix the input pin 12 hysteresis in order to increase immunity to the 100Hz ripple present on the supply voltage.

Moreover, the power fail and reset delay time are automatically locked to the soft-start. Soft-start and delayed reset are thus two sequential functions.

The hysteresis resistor should be In the range of aboit  $100k\Omega$  and the pull-up resistor of 1 to  $2.2k\Omega$ .

Figure 46

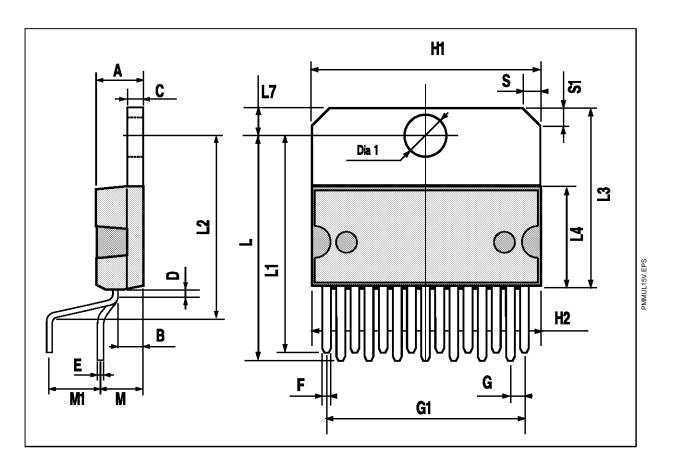

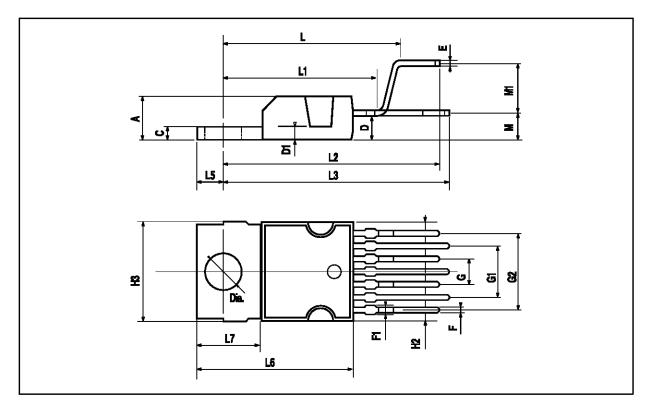

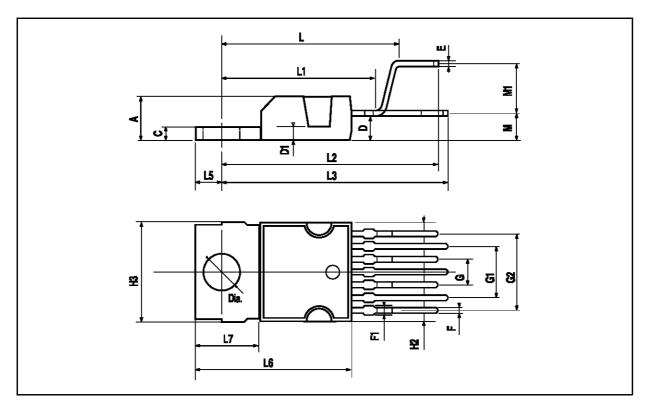

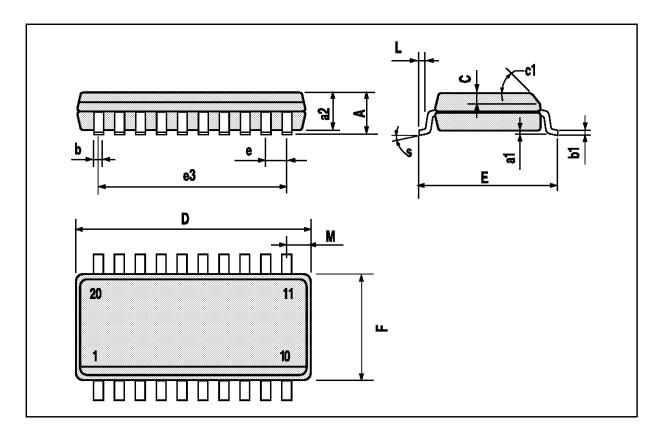

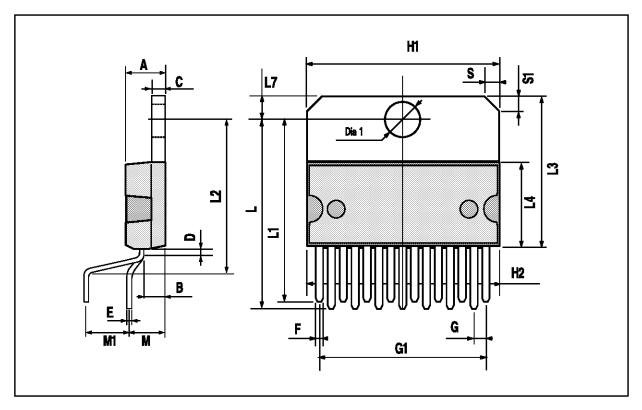

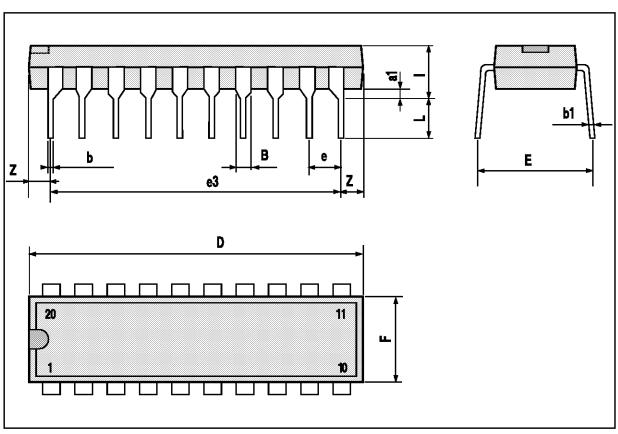

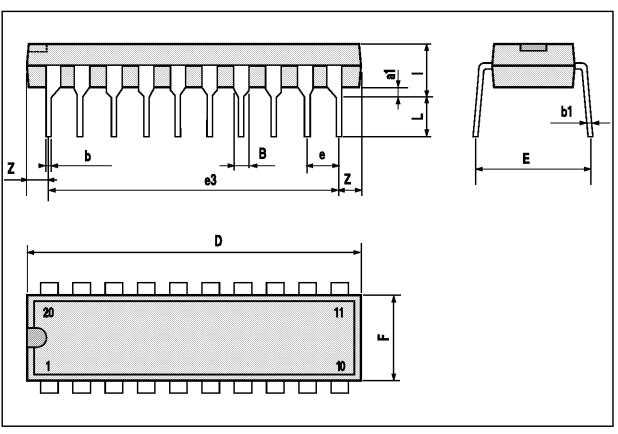

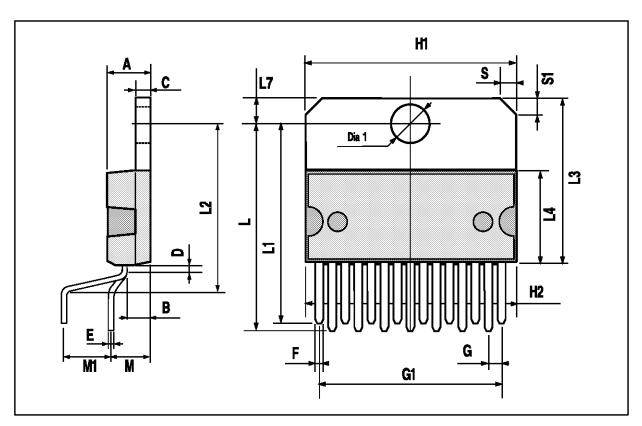

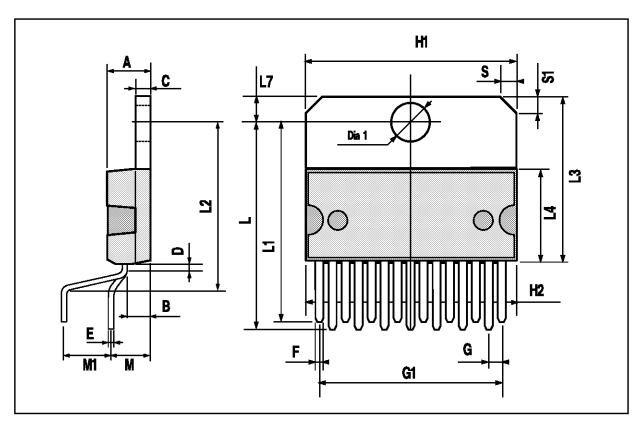

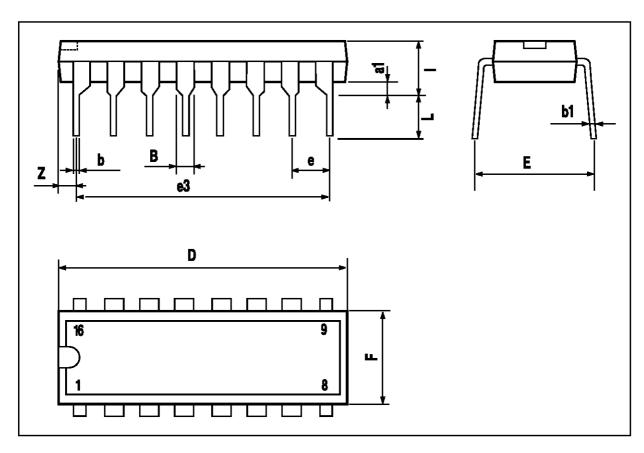

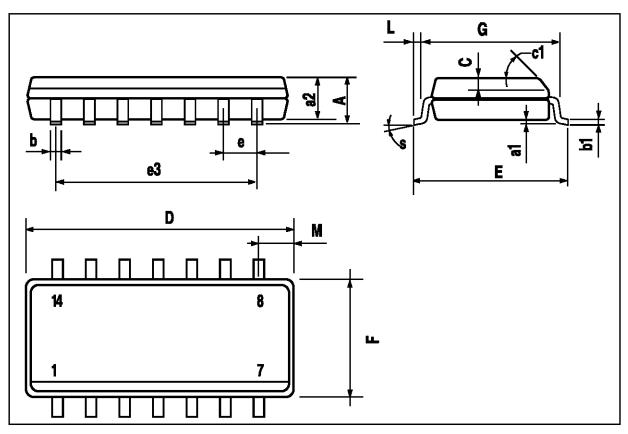

# MULTIWATT15 VERTICAL PACKAGE MECHANICAL DATA

| Dimensions |       | Millimeters |       |       | Inches |       |

|------------|-------|-------------|-------|-------|--------|-------|

| Dimensions | Min.  | Тур.        | Max.  | Min.  | Тур.   | Max.  |

| А          |       |             | 5     |       |        | 0.197 |

| В          |       |             | 2.65  |       |        | 0.104 |

| С          |       |             | 1.6   |       |        | 0.063 |

| D          |       | 1           |       |       | 0.039  |       |

| Е          | 0.49  |             | 0.55  | 0.019 |        | 0.022 |

| F          | 0.66  |             | 0.75  | 0.026 |        | 0.030 |

| G          | 1.14  | 1.27        | 1.4   | 0.045 | 0.050  | 0.055 |

| G1         | 17.57 | 17.78       | 17.91 | 0.692 | 0.700  | 0.705 |

| H1         | 19.6  |             |       | 0.772 |        |       |

| H2         |       |             | 20.2  |       |        | 0.795 |

| L          | 22.1  |             | 22.6  | 0.870 |        | 0.890 |

| L1         | 22    |             | 22.5  | 0.866 |        | 0.886 |

| L2         | 17.65 |             | 18.1  | 0.695 |        | 0.713 |

| L3         | 17.25 | 17.5        | 17.75 | 0.679 | 0.689  | 0.699 |

| L4         | 10.3  | 10.7        | 10.9  | 0.406 | 0.421  | 0.429 |

| L7         | 2.65  |             | 2.9   | 0.104 |        | 0.114 |

| M          | 4.2   | 4.3         | 4.6   | 0.165 | 0.169  | 0.181 |

| M1         | 4.5   | 5.08        | 5.3   | 0.177 | 0.200  | 0.209 |

| S          | 1.9   |             | 2.6   | 0.075 |        | 0.102 |

| S1         | 1.9   |             | 2.6   | 0.075 |        | 0.102 |

| Dia. 1     | 3.65  |             | 3.85  | 0.144 |        | 0.152 |

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.

© 1994 SGS-THOMSON Microelectronics - All Rights Reserved

SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco - The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thaliand - United Kingdom - U.S.A.

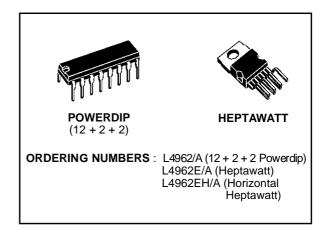

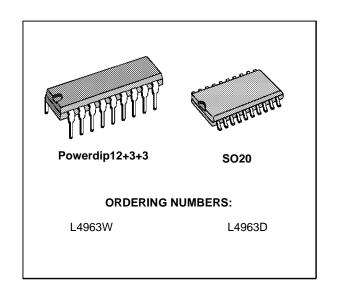

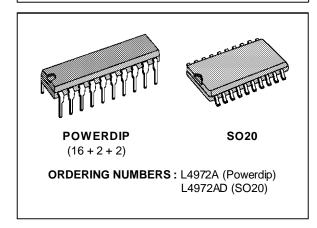

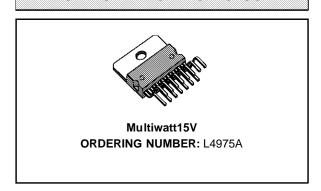

# 2.5A POWER SWITCHING REGULATOR

- 2.5A OUTPUT CURRENT

- 5.1V TO 40V OPUTPUT VOLTAGE RANGE

- PRECISE (± 2%) ON-CHIP REFERENCE

- HIGH SWITCHING FREQUENCY

- VERY HIGH EFFICIENCY (UP TO 90%)

- VERY FEW EXTERNAL COMPONENTS

- SOFT START

- INTERNAL LIMITING CURRENT

- THERMAL SHUTDOWN

The L4960 is a monolithic power switching regulator delivering 2.5A at a voltage variable from 5V to 40V in step down configuration.

Features of the device include current limiting, soft start, thermal protection and 0 to 100% duty cycle for continuous operation mode.

The L4960 is mounted in a Heptawatt plastic power package and requires very few external components.

Efficient operation at switching frequencies up to 150KHz allows a reduction in the size and cost of external filter components.

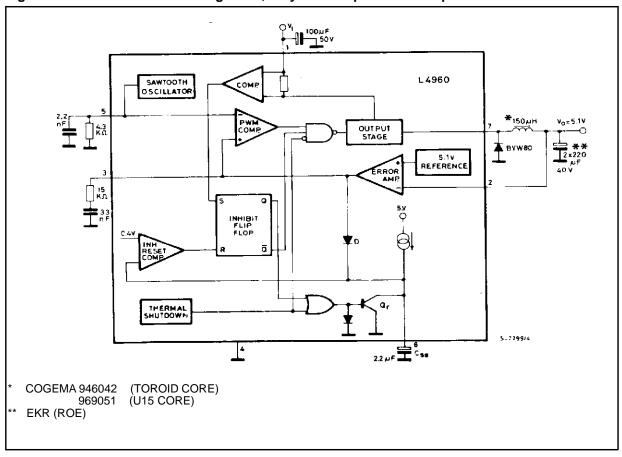

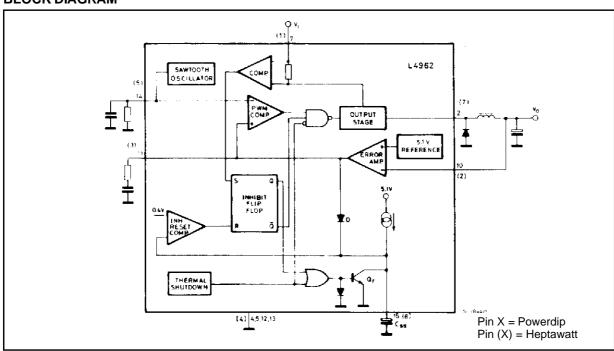

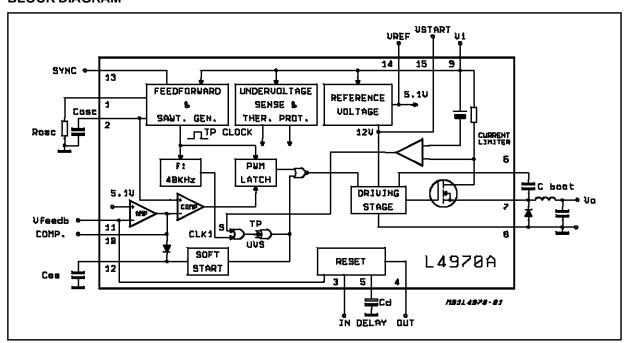

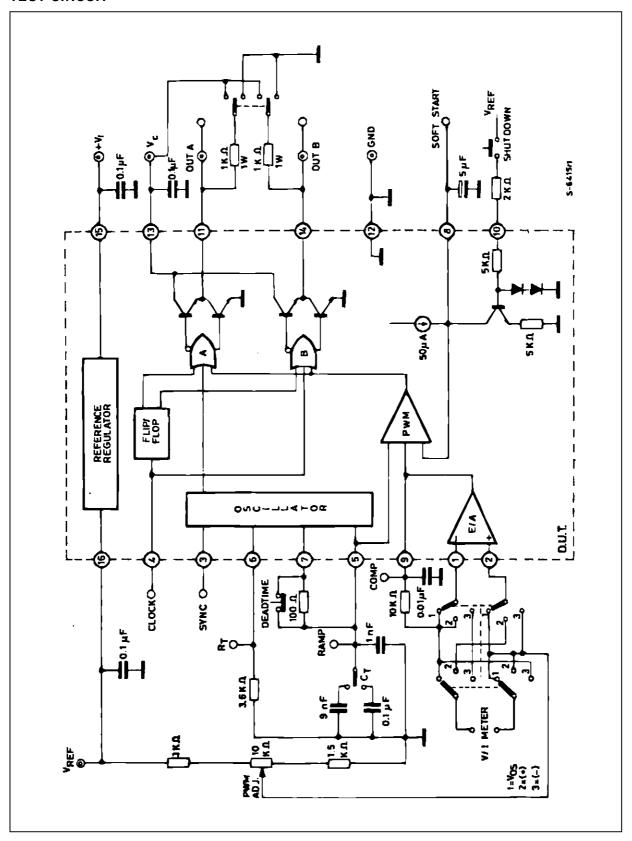

#### **BLOCK DIAGRAM**

April 1995 1/15

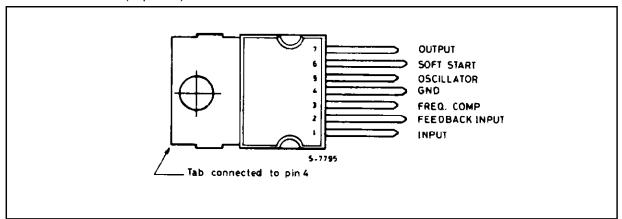

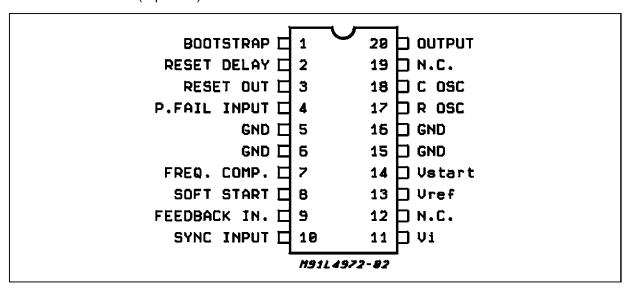

# PIN CONNECTION (Top view)

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                            | Parameter                                             | Value      | Unit |

|-----------------------------------|-------------------------------------------------------|------------|------|

| V <sub>1</sub>                    | Input voltage                                         | 50         | V    |

| V <sub>1</sub> - V <sub>7</sub>   | Input to output voltage difference                    | 50         | V    |

| V <sub>7</sub>                    | Negative output DC voltage                            | -1         | V    |

|                                   | Negative output peak voltage at t = 0.1μs; f = 100KHz | -5         | V    |

| V <sub>3</sub> , V <sub>6</sub>   | Voltage at pin 3 and 6                                | 5.5        | V    |

| V <sub>2</sub>                    | Voltage at pin 2                                      | 7          | V    |

| l <sub>3</sub>                    | Pin 3 sink current                                    | 1          | mA   |

| l <sub>5</sub>                    | Pin 5 source current                                  | 20         | mA   |

| P <sub>tot</sub>                  | Power dissipation at T <sub>case</sub> ≤ 90°C         | 15         | W    |

| T <sub>j</sub> , T <sub>stg</sub> | Junction and storage temperature                      | -40 to 150 | °C   |

# **PIN FUNCTIONS**

| N° | NAME                      | FUNCTION                                                                                                                                                                                             |

|----|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | SUPPLY VOLTAGE            | Unregulated voltage input. An internal regulator powers the internal logic.                                                                                                                          |

| 2  | FEEDBACK INPUT            | The feedback terminal of the regulation loop. The output is connected directly to this terminal for 5.1V operation; it is connected via a divider for higher voltages.                               |

| 3  | FREQUENCY<br>COMPENSATION | A series RC network connected between this terminal and ground determines the regulation loop gain characteristics.                                                                                  |

| 4  | GROUND                    | Common ground terminal.                                                                                                                                                                              |

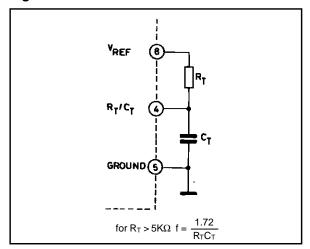

| 5  | OSCILLATOR                | A parallel RC network connected to this terminal determines the switching frequency.                                                                                                                 |

| 6  | SOFT START                | Soft start time constant. A capacitor is connected between this terminal and ground to define the soft start time constant. This capacitor also determines the average short circuit output current. |

| 7  | OUTPUT                    | Regulator output.                                                                                                                                                                                    |

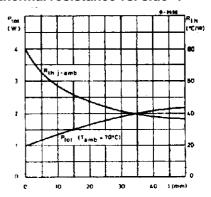

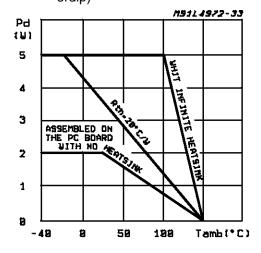

# THERMAL DATA

| Symbol                 | Parameter                               | Value | Unit |

|------------------------|-----------------------------------------|-------|------|

| R <sub>th j-case</sub> | Thermal resistance junction-case max    | 4     | °C/W |

| R <sub>th j-amb</sub>  | Thermal resistance junction-ambient max | 50    | °C/W |

# **ELECTRICAL CHARACTERISTICS** (Refer to the test circuit, $T_j = 25$ °C, $V_i = 35V$ , unless otherwise specified)

| Symbol                                | Parameter                                        | Test Conditions                                                                                            |                               | Min. | Тур. | Max. | Unit  |

|---------------------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------------|------|------|------|-------|

| DYNAMI                                | C CHARACTERISTICS                                |                                                                                                            |                               |      |      |      |       |

| Vo                                    | Output voltage range                             | Vi = 46V                                                                                                   | I <sub>o</sub> = 1A           | Vref |      | 40   | V     |

| Vi                                    | Input voltage range                              | $V_o = V_{ref}$ to 36V                                                                                     | I <sub>o</sub> = 2.5A         | 9    |      | 46   | V     |

| ΔVo                                   | Line regulation                                  | V <sub>i</sub> = 10V to 40V V <sub>c</sub>                                                                 | $_{o} = V_{ref}$ $I_{o} = 1A$ |      | 15   | 50   | mV    |

| ΔVo                                   | Load regulation                                  | $V_{o} = V_{ref}$                                                                                          | I <sub>o</sub> = 0.5A to 2A   |      | 10   | 30   | mV    |

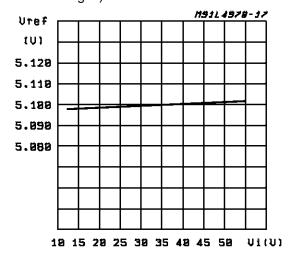

| V <sub>ref</sub>                      | Internal reference voltage (pin 2)               | V <sub>i</sub> = 9V to 46V                                                                                 | I <sub>o</sub> = 1A           | 5    | 5.1  | 5.2  | V     |

| $\frac{\Delta \ V_{ref}}{\Delta \ T}$ | Average temperature coefficient of refer voltage | $T_j = 0$ °C to 125°C $I_o = 1$ A                                                                          |                               |      | 0.4  |      | mV/°C |

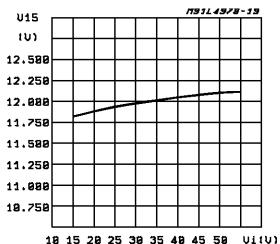

| V <sub>d</sub>                        | Dropout voltage                                  | I <sub>0</sub> = 2A                                                                                        |                               |      | 1.4  | 3    | V     |

| I <sub>om</sub>                       | Maximum operating load current                   | V <sub>i</sub> = 9V to 46V<br>V <sub>o</sub> = V <sub>ref</sub> to 36V                                     |                               | 2.5  |      |      | А     |

| I <sub>7L</sub>                       | Current limiting threshold (pin 7)               | V <sub>i</sub> = 9V to 46V<br>V <sub>o</sub> = V <sub>ref</sub> to 36V                                     |                               | 3    |      | 4.5  | А     |

| I <sub>SH</sub>                       | Input average current                            | V <sub>i</sub> = 46V; output s                                                                             | short-circuit                 |      | 30   | 60   | mA    |

| η                                     | Efficiency                                       | f = 100KHz                                                                                                 | $V_0 = V_{ref}$               |      | 75   |      | %     |

|                                       |                                                  | I <sub>0</sub> = 2A                                                                                        | V <sub>o</sub> = 12V          |      | 85   |      | %     |

| SVR                                   | Supply voltage ripple rejection                  | $\begin{array}{l} \Delta \ V_i = 2 V_{rms} \\ \text{fripple} = 100 \text{Hz} \\ V_o = V_{ref} \end{array}$ | lo = 1A                       | 50   | 56   |      | dB    |

| f                                     | Switching frequency                              |                                                                                                            |                               | 85   | 100  | 115  | KHz   |

| $\frac{\Delta f}{\Delta V_i}$         | Voltage stability of switching frequency         | V <sub>i</sub> = 9V to 46V                                                                                 |                               |      | 0.5  |      | %     |

| $\frac{\Delta f}{\Delta T_j}$         | Temperature stability of switching frequency     | T <sub>j</sub> = 0°C to 125°C                                                                              |                               |      | 1    |      | %     |

| f <sub>max</sub>                      | Maximum operating switching frequency            | $V_o = V_{ref}$                                                                                            | I <sub>0</sub> = 2A           | 120  | 150  |      | KHz   |

| T <sub>sd</sub>                       | Thermal shutdown junction temperature            |                                                                                                            |                               |      | 150  |      | °C    |

# **ELECTRICAL CHARACTERISTICS** (continued)

| Symbol            | Parameter                 | Test Conditions                      |                        | Min. | Тур. | Max. | Unit |

|-------------------|---------------------------|--------------------------------------|------------------------|------|------|------|------|

| C CHA             | RACTERISTICS              |                                      |                        |      |      |      |      |

| I <sub>1Q</sub>   | Quiescent drain current   | 100% duty cycle<br>pins 5 and 7 open | )/ 46\/                |      | 30   | 40   | mA   |

|                   |                           | 0% duty cycle                        | V <sub>i</sub> = 46V   |      | 15   | 20   | mA   |

| -l <sub>7L</sub>  | Output leakage current    | 0% duty cycle                        |                        |      |      | 1    | mA   |

| OFT ST            | TART                      |                                      |                        |      |      |      |      |

| I <sub>6SO</sub>  | Source current            |                                      |                        | 100  | 140  | 180  | μА   |

| I <sub>6SI</sub>  | Sink current              |                                      |                        | 50   | 70   | 120  | μА   |

| RROR              | AMPLIFIER                 | •                                    |                        |      |      |      |      |

| V <sub>3H</sub>   | High level output voltage | V <sub>2</sub> = 4.7V                | I <sub>3</sub> = 100μA | 3.5  |      |      | V    |

| V <sub>3L</sub>   | Low level output voltage  | V <sub>2</sub> = 5.3V                | I <sub>3</sub> = 100μA |      |      | 0.5  | ٧    |

| I <sub>3SI</sub>  | Sink output current       | V <sub>2</sub> = 5.3V                |                        | 100  | 150  |      | μА   |

| -I <sub>3SO</sub> | Source output current     | V <sub>2</sub> = 4.7V                |                        | 100  | 150  |      | μΑ   |

| l <sub>2</sub>    | Input bias current        | V <sub>2</sub> = 5.2V                |                        |      | 2    | 10   | μА   |

| G <sub>v</sub>    | DC open loop gain         | V <sub>3</sub> = 1V to 3V            |                        | 46   | 55   |      | dB   |

| SCILLA            | ATOR                      | •                                    |                        | •    |      |      | •    |

| -l <sub>5</sub>   | Oscillator source current |                                      |                        | 5    |      |      | mA   |

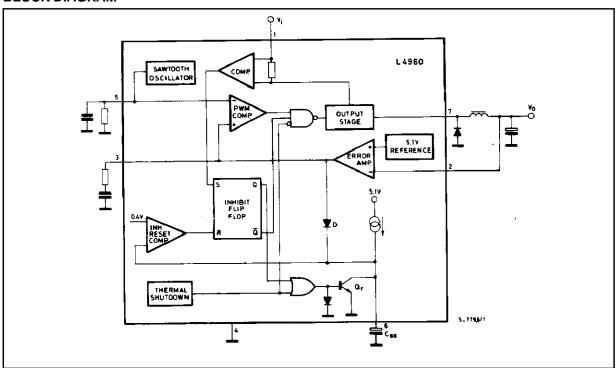

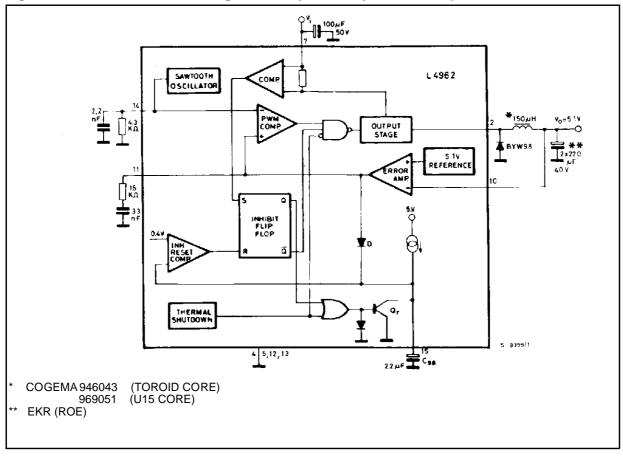

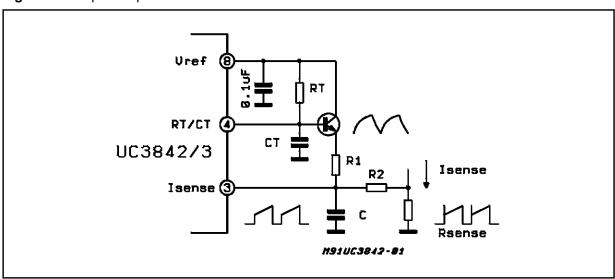

#### **CIRCUIT OPERATION** (refer to the block diagram)

The L4960 is a monolithic stepdown switching regulator providing output voltages from 5.1V to 40V and delivering 2.5A.

The regulation loop consists of a sawtooth oscillator, error amplifier, comparator and the output stage. An error signal is produced by comparing the output voltage with a precise 5.1V on-chip reference (zener zap trimmed to  $\pm$  2%).

This error signal is then compared with the sawtooth signal to generate the fixed frequency pulse width modulated pulses which drive the output stage.

The gain and frequency stability of the loop can be adjusted by an external RC network connected to pin 3. Closing the loop directly gives an output voltage of 5.1V. Higher voltages are obtained by inserting a voltage divider.

Output overcurrents at switch on are prevented by the soft start function. The error amplifier output is initially clamped by the external capacitor C<sub>ss</sub> and allowed to rise, linearly, as this capacitor is charged by a constant current source. Output overload protection is provided in the form of a current limiter. The load current is sensed by an internal metal resistor connected to a comparator. When the load current exceeds a preset threshold this comparator sets a flip flop which disables the output stage and discharges the soft start capacitor. A second comparator resets the flip flop when the voltage across the soft start capacitor has fallen to 0.4V.

The output stage is thus re-enabled and the output voltage rises under control of the soft start network. If the overload condition is still present the limiter will trigger again when the threshold current is reached. The average short circuit current is limited to a safe value by the dead time introduced by the soft start network. The thermal overload circuit disables circuit operation when the junction temperature reaches about 150°C and has hysteresis to prevent unstable conditions.

Figure 2. Current limiter waveforms

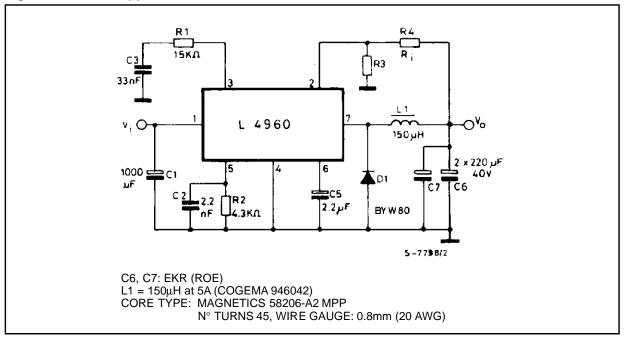

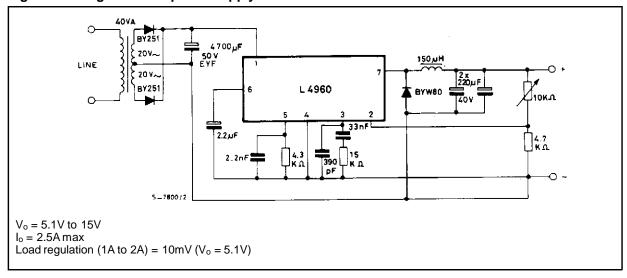

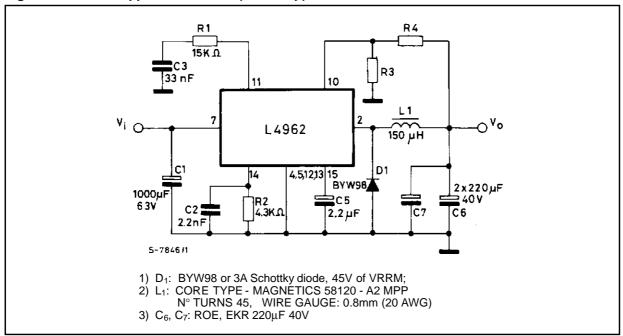

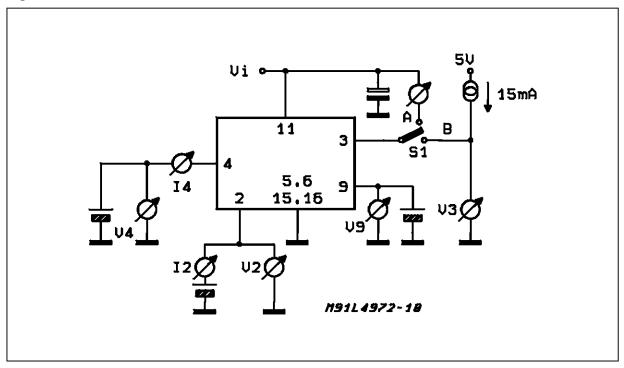

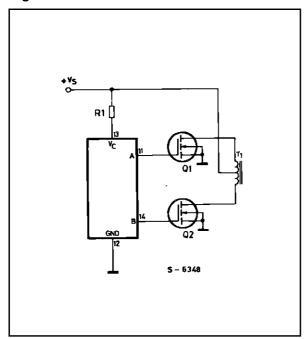

Figure 3. Test and application circuit

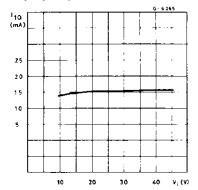

Figure 4. Quiescent drain current vs. supply voltage (0% duty cycle)

Figure 5. Quiescent drain current vs. supply voltage (100% duty cycle)

Figure 6. Quiescent drain current vs. junction temperature (0% duty cycle)

Figure 7. Quiescent drain current vs. junction temperature (100% duty cycle)

Figure 8. Reference voltage (pin 2) vs. V<sub>i</sub>

Figure 9. Reference voltage versus junction temperature (pin 2)

Figure 10. Open loop frequency and phase responde of error amplifier

Figure 11. Switching frequency vs. input voltage

Figure 12. Switching frequency vs. junction temperature

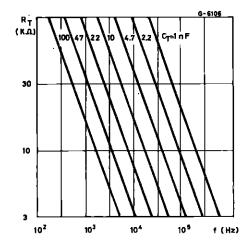

Figure 13. Switching frequency vs. R2 (see test circuit)

Figure 14. Line transient response

Figure 15. Load transient response

Figure 16. Supply voltage ripple rejection vs. frequency

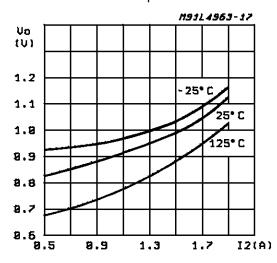

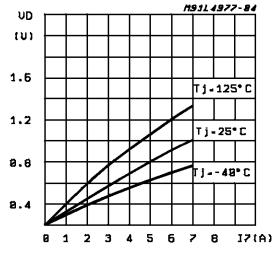

Figure 17. Dropout voltage between pin 1 and pin 7 vs. current at pin 7

Figure 18. Dropout voltage between pin 1 and 7 vs. junction temperature

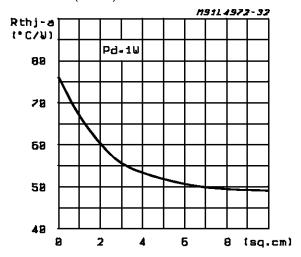

Figure 19. Power dissipation derating curve

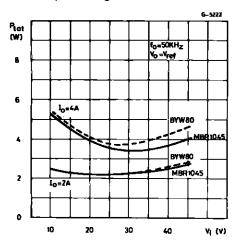

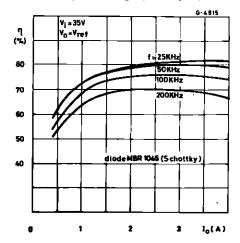

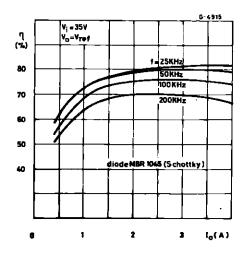

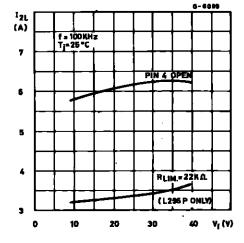

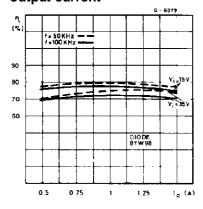

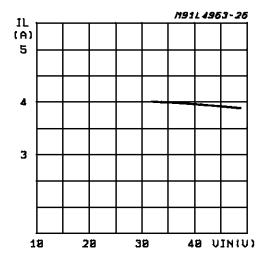

Figure 20. Efficiency vs. output current

Figure 21. Efficiency vs. output current

Figure 22. Efficiency vs. output current

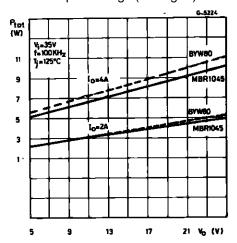

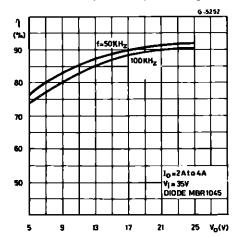

Figure 23. Efficiency vs. output voltage

#### **APPLICATION INFORMATION**

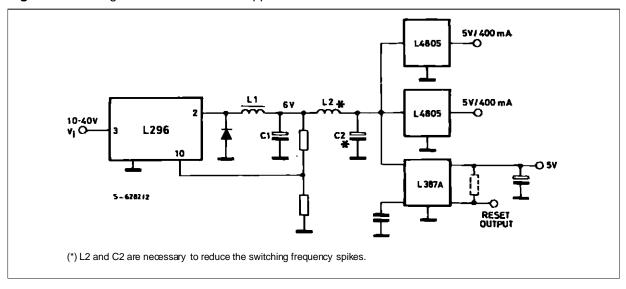

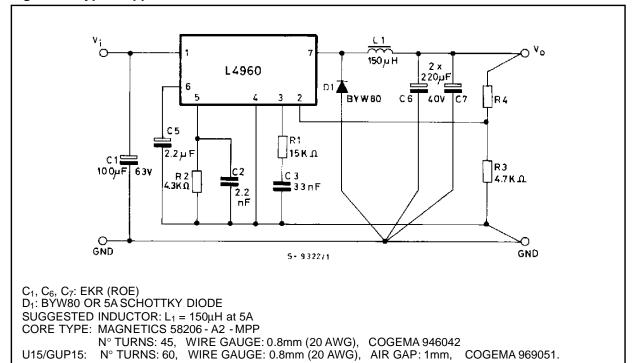

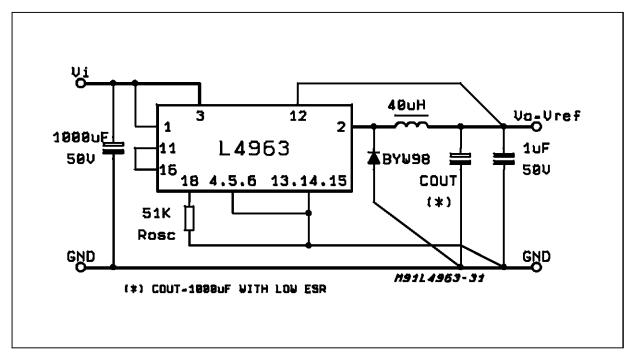

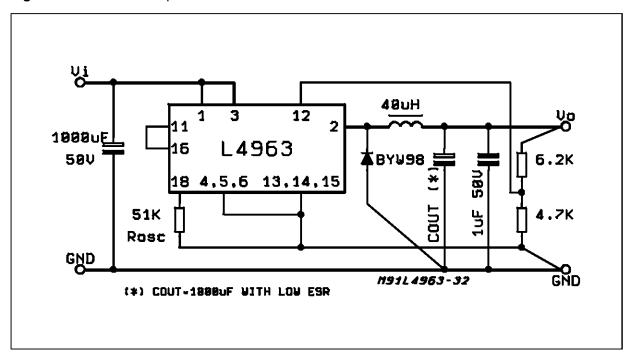

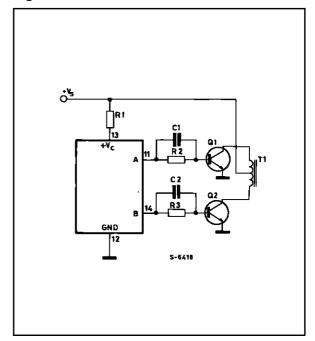

Figure 24. Typical application circuit

Figure 25. P.C. board and component layout of the Fig. 24 (1:1 scale)

|                          | Resistor values for andard output voltages |                                |  |  |  |  |

|--------------------------|--------------------------------------------|--------------------------------|--|--|--|--|

| Vo                       | R3                                         | R4                             |  |  |  |  |

| 12V<br>15V<br>18V<br>24V | 4.7KΩ<br>4.7KΩ<br>4.7KΩ<br>4.7KΩ           | 6.2KΩ<br>9.1KΩ<br>12KΩ<br>18KΩ |  |  |  |  |

#### **APPLICATION INFORMATION**

Figure 26. A minimal 5.1V fixed regulator; Very few component are required

Figure 27. Programmable power supply

# **APPLICATION INFORMATION** (continued)

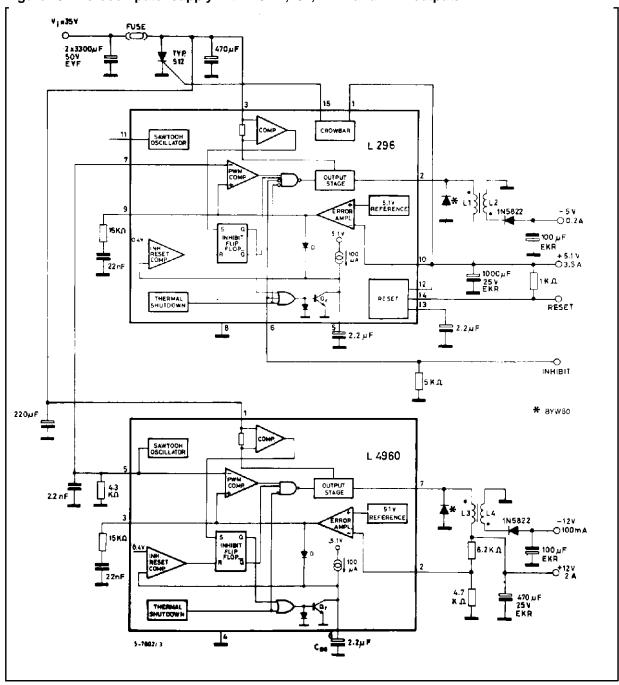

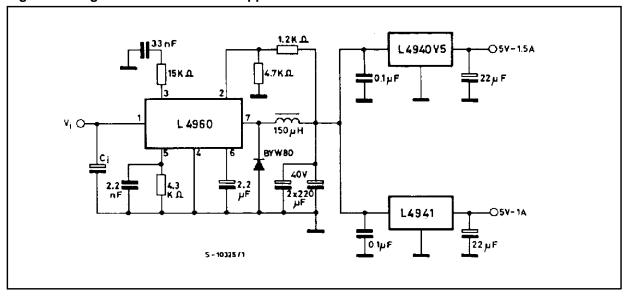

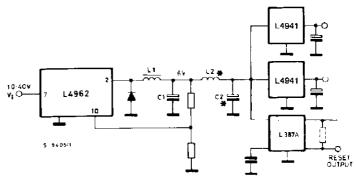

Figure 28. Microcomputer supply with + 5.1V, -5V, +12V and -12V outputs

#### **APPLICATION INFORMATION (continued)**

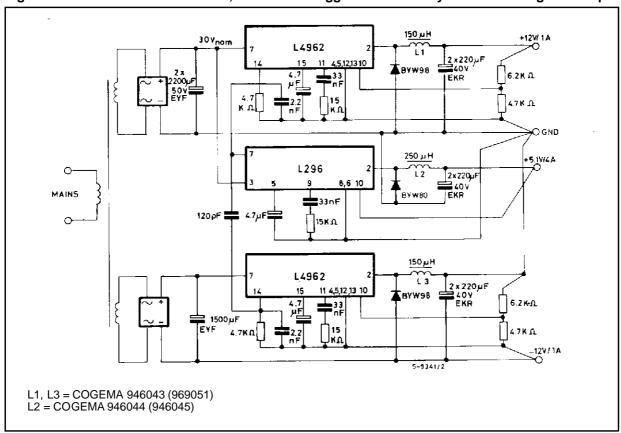

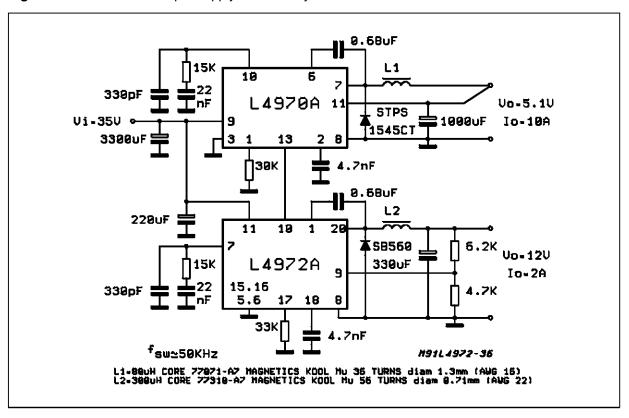

Figure 29. DC-DC converter  $5.1V/4A, \pm 12V/2.5A$ ; a suggestion how to synchronize a negative output

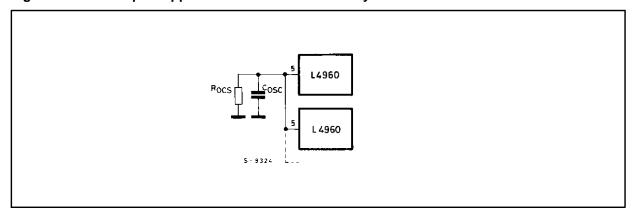

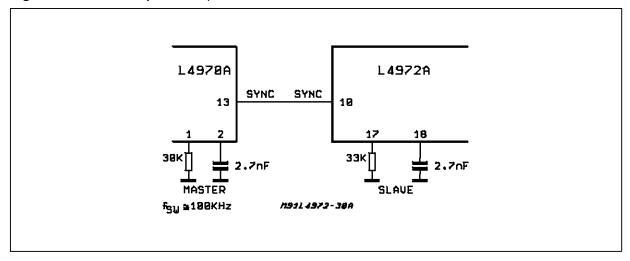

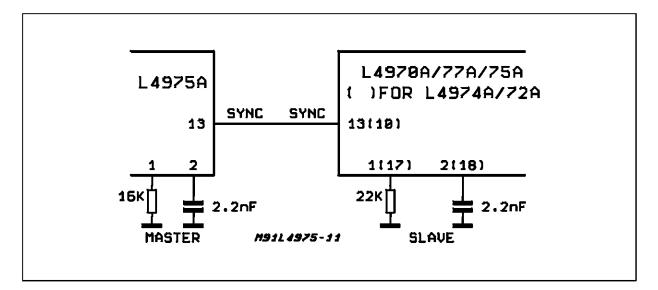

Figure 30. - In multiple supplies several L4960s can be synchronized as shown

#### **APPLICATION INFORMATION** (continued)

Figure 31. Regulator for distributed supplies

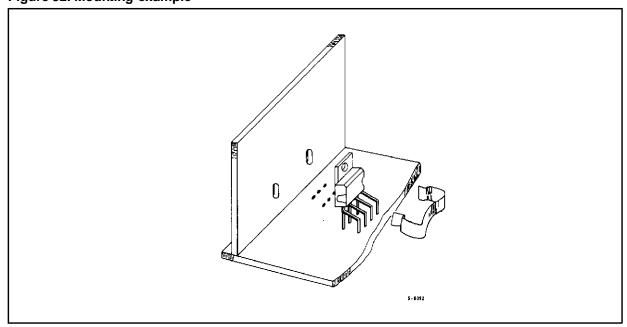

#### **MOUNTING INSTRUCTION**

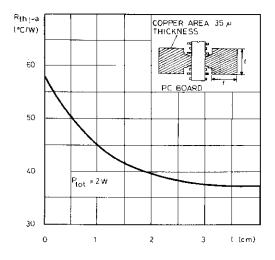

The power dissipated in the circuit must be removed by adding an external heatsink.

Thanks to the Heptawatt package attaching the hetsink is very simple, a screw or a compression spring (clip) being sufficient. Between the heatsink

and the package it is better to insert a layer of silicon grease, to optimize the thermal contact, no electrical isolation is needed between the two surfaces.

Figure 32. Mounting example

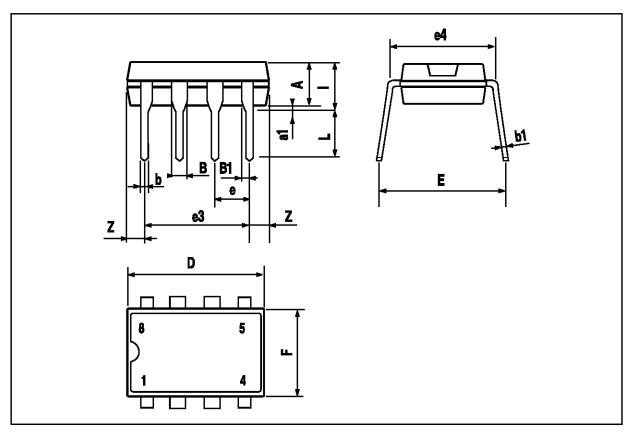

# **HEPTAWATT PACKAGE MECHANICAL DATA**

| DIM.  | mm    |       |      | inch  |       |       |  |

|-------|-------|-------|------|-------|-------|-------|--|

| DIWI. | MIN.  | TYP.  | MAX. | MIN.  | TYP.  | MAX.  |  |

| Α     |       |       | 4.8  |       |       | 0.189 |  |

| С     |       |       | 1.37 |       |       | 0.054 |  |

| D     | 2.4   |       | 2.8  | 0.094 |       | 0.110 |  |

| D1    | 1.2   |       | 1.35 | 0.047 |       | 0.053 |  |

| Е     | 0.35  |       | 0.55 | 0.014 |       | 0.022 |  |

| F     | 0.6   |       | 0.8  | 0.024 |       | 0.031 |  |

| F1    |       |       | 0.9  |       |       | 0.035 |  |

| G     | 2.41  | 2.54  | 2.67 | 0.095 | 0.100 | 0.105 |  |

| G1    | 4.91  | 5.08  | 5.21 | 0.193 | 0.200 | 0.205 |  |

| G2    | 7.49  | 7.62  | 7.8  | 0.295 | 0.300 | 0.307 |  |

| H2    |       |       | 10.4 |       |       | 0.409 |  |

| H3    | 10.05 |       | 10.4 | 0.396 |       | 0.409 |  |

| L     |       | 16.97 |      |       | 0.668 |       |  |

| L1    |       | 14.92 |      |       | 0.587 |       |  |

| L2    |       | 21.54 |      |       | 0.848 |       |  |

| L3    |       | 22.62 |      |       | 0.891 |       |  |

| L5    | 2.6   |       | 3    | 0.102 |       | 0.118 |  |

| L6    | 15.1  |       | 15.8 | 0.594 |       | 0.622 |  |

| L7    | 6     |       | 6.6  | 0.236 |       | 0.260 |  |

| М     |       | 2.8   |      |       | 0.110 |       |  |

| M1    |       | 5.08  |      |       | 0.200 |       |  |

| Dia   | 3.65  |       | 3.85 | 0.144 |       | 0.152 |  |

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.

© 1995 SGS-THOMSON Microelectronics - All Rights Reserved

SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco - The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thaliand - United Kingdom - U.S.A.

# 1.5A POWER SWITCHING REGULATOR

- 1.5A OUTPUT CURRENT

- 5.1V TO 40V OUTPUT VOLTAGE RANGE

- PRECISE (± 2%) ON-CHIP REFERENCE

- HIGH SWITCHING FREQUENCY

- VERY HIGH EFFICIENCY (UP TO 90%)

- VERY FEW EXTERNAL COMPONENTS

- SOFT START

- INTERNAL LIMITING CURRENT

- THERMAL SHUTDOWN

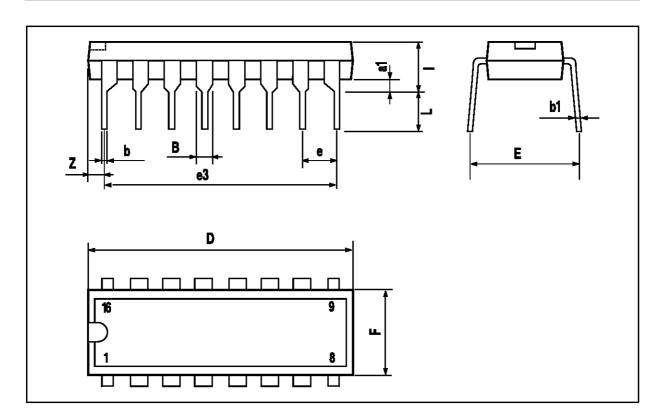

#### **DESCRIPTION**

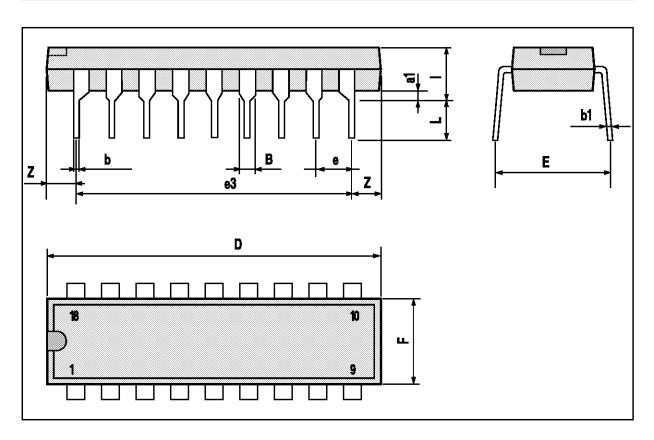

The L4962 is a monolithic power switching regulator delivering 1.5A at a voltage variable from 5V to 40V in step down configuration.

Features of the device include current limiting, soft start, thermal protection and 0 to 100% duty cycle for continuous operating mode.

The L4962 is mounted in a 16-lead Powerdip plastic package and Heptawatt package and requires very few external components.

Efficient operation at switching frequencies up to 150KHz allows a reduction in the size and cost of external filter components.

#### **BLOCK DIAGRAM**

March 1996 1/15

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                            | Parameter                                                                                | Value      | Unit   |

|-----------------------------------|------------------------------------------------------------------------------------------|------------|--------|

| V <sub>7</sub>                    | Input voltage                                                                            | 50         | V      |

| V <sub>7</sub> - V <sub>2</sub>   | Input to output voltage difference                                                       | 50         | V      |

| V <sub>2</sub>                    | Negative output DC voltage                                                               | -1         | V      |

|                                   | Output peak voltage at t = 0.1μs; f = 100KHz                                             | -5         | V      |

| V <sub>11</sub> , V <sub>15</sub> | Voltage at pin 11, 15                                                                    | 5.5        | V      |

| V <sub>10</sub>                   | Voltage at pin 10                                                                        | 7          | V      |

| I <sub>11</sub>                   | Pin 11 sink current                                                                      | 1          | mA     |

| I <sub>14</sub>                   | Pin 14 source current                                                                    | 20         | mA     |

| P <sub>tot</sub>                  | Power dissipation at $T_{pins} \le 90$ °C (Powerdip)<br>$T_{case} \le 90$ °C (Heptawatt) | 4.3<br>15  | W<br>W |

| Tj, Tstg                          | Junction and storage temperature                                                         | -40 to 150 | °C     |

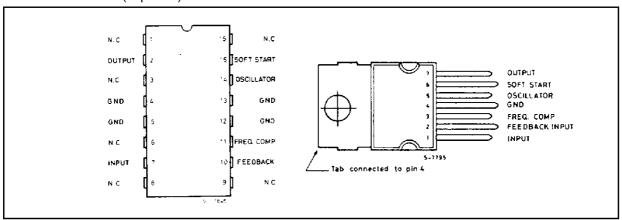

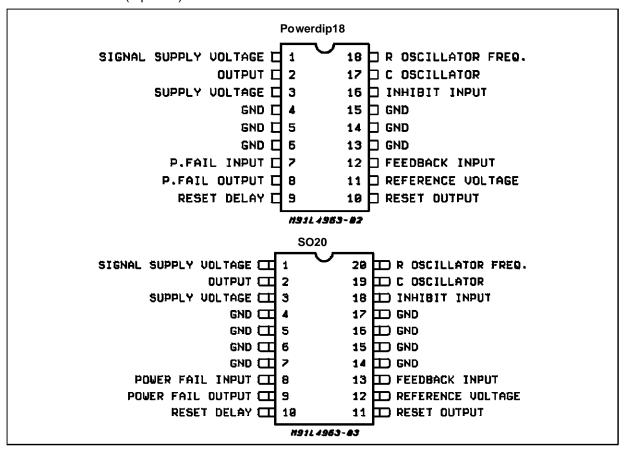

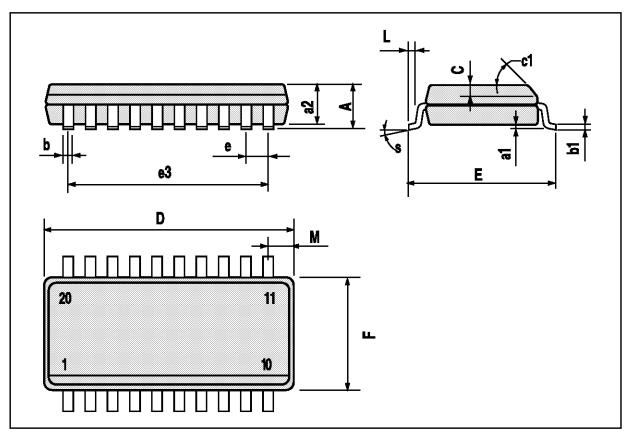

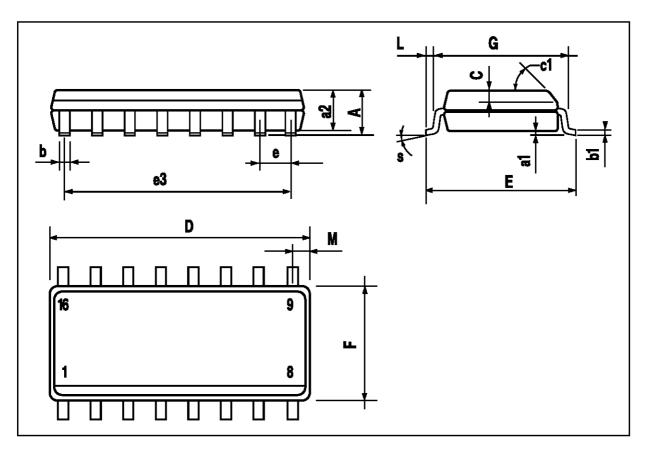

#### PIN CONNECTION (Top view)

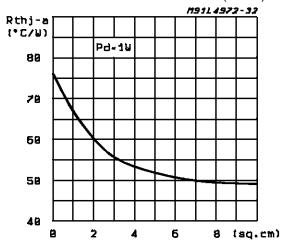

#### THERMAL DATA

| Symbol                 | Parameter                               | Heptawatt | Powerdip |

|------------------------|-----------------------------------------|-----------|----------|

| R <sub>th j-case</sub> | Thermal resistance junction-case max    | 4°C/W     | -        |

| R <sub>th i-pins</sub> | Thermal resistance junction-pins max    | -         | 14°C/W   |

| R <sub>th j-amb</sub>  | Thermal resistance junction-ambient max | 50°C/W    | 80°C/W*  |

<sup>\*</sup> Obtained with the GND pins soldered to printed circuit with minimized copper area.

#### **PIN FUNCTIONS**

| HEPTAWATT | POWERDIP | NAME                      | FUNCTION                                                                                                                                                               |

|-----------|----------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1         | 7        | SUPPLY VOLTAGE            | Unregulated voltage input. An internal regulator powers the internal logic.                                                                                            |

| 2         | 10       | FEEDBACK INPUT            | The feedback terminal of the regulation loop. The output is connected directly to this terminal for 5.1V operation; it is connected via a divider for higher voltages. |

| 3         | 11       | FREQUENCY<br>COMPENSATION | A series RC network connected between this terminal and ground determines the regulation loop gain characteristics.                                                    |

## PIN FUNCTIONS (cont'd)

| HEPTAWATT | POWERDIP             | NAME       | FUNCTION                                                                                                                                                                                             |

|-----------|----------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4         | 4, 5, 12, 13         | GROUND     | Common ground terminal.                                                                                                                                                                              |

| 5         | 14                   | OSCILLATOR | A parallel RC network connected to this terminal determines the switching frequency. This pin must be connected to pin 7 input when the internal oscillator is used.                                 |

| 6         | 15                   | SOFT START | Soft start time constant. A capacitor is connected between this terminal and ground to define the soft start time constant. This capacitor also determines the average short circuit output current. |

| 7         | 2                    | OUTPUT     | Regulator output.                                                                                                                                                                                    |

|           | 1, 3, 6,<br>8, 9, 16 |            | N.C.                                                                                                                                                                                                 |

# **ELECTRICAL CHARACTERISTICS** (Refer to the test circuit, $T_j$ = 25 °C, $V_i$ = 35V, unless otherwise specified)

| Symbol                            | Parameter                                         | Test Condition s                                                                                    |                               |           | Тур. | Max.  | Unit |

|-----------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------|-----------|------|-------|------|

| DYNAMI                            | C CHARACTERISTICS                                 |                                                                                                     |                               |           |      |       |      |

| Vo                                | Output voltage range                              | V <sub>i</sub> = 46V                                                                                | I <sub>0</sub> = 1A           | $V_{ref}$ |      | 40    | V    |

| Vi                                | Input voltage range                               | V <sub>o</sub> = V <sub>ref</sub> to 36V                                                            | I <sub>o</sub> = 1.5A         | 9         |      | 46    | V    |

| ΔVo                               | Line regulation                                   | $V_i = 10V \text{ to } 40V  V_o$                                                                    | $= V_{ref}$ $I_0 = 1A$        |           | 15   | 50    | mV   |

| ΔVo                               | Load regulation                                   | $V_o = V_{ref}$                                                                                     | $I_0 = 0.5A \text{ to } 1.5A$ |           | 8    | 20    | mV   |

| $V_{ref}$                         | Internal reference voltage (pin 10)               | V <sub>i</sub> = 9V to 46V                                                                          | 5                             | 5.1       | 5.2  | ٧     |      |

| $\frac{\Delta V_{ref}}{\Delta T}$ | Average temperature coefficient of refer. voltage | $T_j = 0$ °C to 125°C $I_0 = 1$ A                                                                   |                               | 0.4       |      | mV/°C |      |

| $V_d$                             | Dropout voltage                                   | I <sub>o</sub> = 1.5A                                                                               |                               | 1.5       | 2    | V     |      |

| l <sub>om</sub>                   | Maximum operating load current                    | V <sub>i</sub> = 9V to 46V<br>V <sub>o</sub> = V <sub>ref</sub> to 36V                              |                               |           |      |       | А    |

| I <sub>2L</sub>                   | Current limiting threshold (pin 2)                | $V_i = 9V \text{ to } 46V$<br>$V_o = V_{ref} \text{ to } 36V$                                       | 2                             |           | 3.3  | А     |      |

| I <sub>SH</sub>                   | Input average current                             | $V_i = 46V$ ; output s                                                                              |                               | 15        | 30   | mA    |      |

| η                                 | Efficiency                                        | f = 100KHz                                                                                          | $V_o = V_{ref}$               |           | 70   |       | %    |

|                                   |                                                   | I <sub>o</sub> = 1A                                                                                 | V <sub>o</sub> = 12V          |           | 80   |       | %    |

| SVR                               | Supply voltage ripple rejection                   | $\begin{array}{l} \Delta \ V_i = 2 V_{rms} \\ \text{fripple} = 100 Hz \\ V_o = V_{ref} \end{array}$ | lo = 1A                       | 50        | 56   |       | dB   |

# **ELECTRICAL CHARACTERISTICS** (continued)

| Symbol                           | Parameter                                    | Test Co                               | Min.                    | Тур. | Max. | Unit |     |  |  |

|----------------------------------|----------------------------------------------|---------------------------------------|-------------------------|------|------|------|-----|--|--|

| DYNAMIC CHARACTERISTICS (cont'd) |                                              |                                       |                         |      |      |      |     |  |  |

| f                                | Switching frequency                          |                                       |                         | 85   | 100  | 115  | KHz |  |  |

| $\frac{\Delta  f}{\Delta  V_i}$  | Voltage stability of switching frequency     | V <sub>i</sub> = 9V to 46V            |                         |      | 0.5  |      | %   |  |  |

| $\frac{\Deltaf}{\DeltaT_j}$      | Temperature stability of switching frequency | $T_j = 0$ °C to 125°C                 |                         |      | 1    |      | %   |  |  |

| f <sub>max</sub>                 | Maximum operating switching frequency        | V <sub>o</sub> = V <sub>ref</sub>     | I <sub>0</sub> = 1A     | 120  | 150  |      | KHz |  |  |