- 4-Bit Slice is Cascadable to N-Bits

- Designed Specifically for Microcontroller/ Next-Address Generator Functions

- Increment/Decrement by One (Immediate or Direct Symbolic Addressing Modes)

- Offset, Vector, or Branch (Indexed or Relative Addressing Modes)

- Store Up to Four Returns or Links (Program Return Address from Subroutine)

- Program start or Initialize (Return to Zero or Clear Mode)

- On-Chip Edge-Triggered Output Register (Provides Steady-State Micro-Address/ Instruction)

- High-Density 20-Pin Dual-in-Line Package with 300-Mil Row Pin Spacing

#### description

The 'S482 is a high-performance Schottky TTL 4-bit-slice control element for use in any computer/control application requiring the coupling of high-performance bipolar speeds with the flexibility of microprogram control and bit-slice expandability. When used as a next-address generator, two 'S482 elements can address up to 256 words of microprogram; three elements can address up to 4096 words of microprogram; or a number of 'S482 elements can generate N words in multiples of four lines.

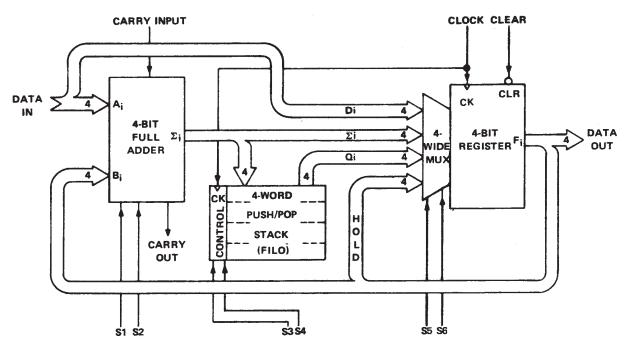

Comprised of an output register, push-pop stack, and a full adder, the 'S482 provides the capability to implement multiway testing needed to generate or to determine and select the source of the next function of microprogram address.

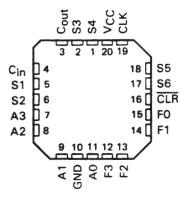

\$N54\$482 . . . J PACKAGE \$N74\$482 . . . J OR N PACKAGE (TOP VIEW)

SN54S482 . . . FH PACKAGE SN74S482 . . . FN PACKAGE (TOP VIEW)

# functional block diagram

# output register and source functions

The 4-bit edge-triggered register provides a steady-state output throughout each system clock cycle. An asynchronous clear extends the multiway testing to directly implement system initialization at ROM address zero.

Two source-select lines (S5, S6) provide the output register with access to either the current instruction (no change), an operand or address stored in the push-pop stack, the output of a four-function full adder, or a direct data-in address port. The sources and functions are summarized in Table I and II.

In bus applications, provision must be made to control negative spikes. When low, the output latches can be disturbed if the outputs are forced more negative than -0.5 V.

TABLE I. REGISTER-SOURCE FUNCTIONS

| SEL        | .ECT | REGISTER INPUT SOURCE       |

|------------|------|-----------------------------|

| <b>S</b> 5 | S6   | REGISTER INPUT SOURCE       |

| L          | L    | DATA-IN PORT (Di)           |

| L          | Н    | FULL ADDER OUTPUTS (Σi)     |

| н          | L    | PUSH-POP STACK OUTPUTS (Qi) |

| н          | Н    | REGISTER OUTPUTS (HOLD)     |

H = high level, L = low level

|          |           |    |            | IN | PUTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | INTERNAL          | OUTPUTS |

|----------|-----------|----|------------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------|---------|

|          | <b>S3</b> | S4 | <b>S</b> 5 | S6 | CLOCK         CLEAR         INTERNA           L         H         QiA0           X         L         QiA0           †         H         QiA0°           †         H         Xi*           †         H         Xi*           †         H         QiB0°           †         H         QiB0°           †         H         QiB0°           †         H         Xi*           †         H         Xi*           †         H         Xi*           †         H         Xi* | QiA | Fi                |         |

| HOLD     | X         | Х  | Х          | X  | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Н   | QiA0              | Fi0     |

| CLEAR    | Х         | X  | X          | Х  | Х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | L   | QiA0              | L       |

| PUSH-POP | L         | L  | L          | L  | Ť                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Н   | QiA0*             | Di      |

| STACK    | L         | L  | L          | Н  | Ť                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Н   | QiA0*             | Σi      |

| "HOLD"   | L         | L  | Н          | L  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Н   | QiA0*             | QiA0    |

| 11025    | L         | L  | н          | Н  | t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Н   | QiA0*             | Fi0     |

| PUSH-POP | L         | Н  | L          | L  | †                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Н   | Σi*               | Di      |

| STACK    | L         | Н  | L          | Н  | †                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Н   | Σi*               | Σί      |

| "LOAD"   | L         | Н  | H          | L  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Н   | Σi*               | QiA0    |

|          | L         | Н  | H          | Н  | †                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Н   | Σi*               | * Fi0   |

| PUSH-POP | Н         | L  | L          | L  | t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Н   | QiB0 <sup>†</sup> | Di      |

| STACK    | Н         | L  | L          | Н  | t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | H   | QiB0 <sup>†</sup> | Σί      |

| "POP"    | Н         | L  | Н          | L  | †                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Н   | QiB0 <sup>†</sup> | QiA0    |

| Ι,       | Н         | L  | Н          | Н  | †                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Н   | QiB0 <sup>†</sup> | Fi0     |

| PUSH-POP | Н         | Н  | L          | L  | †                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Н   | Σi‡               | Di      |

| STACK    | Н         | Н  | L          | Н  | t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Н   | Σi‡               | Σί      |

| "PUSH"   | Н         | н  | Н          | L  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Н   | Σi‡               | QiA0    |

| . 5511   | Н         | Н  | н          | н  | t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Н   | Σi‡               | Fi0     |

TABLE II. PUSH-POP STACK CONTROL AND REGISTER-SOURCE FUNCTIONS

MSB LSB i = 3, 2, 1, 0

Ai = Data inputs

QiA = Push-pop stack word A output (internal)

QiAO = the level of Qi before the indicated inputs conditions were established.

FiO = the level of Fi before the indicated input conditions were established

$\Sigma i = Adder outputs (internal)$

\*QiB, QiC, QiD do not change

<sup>†</sup>QiDO → QiD, QiDO → QiC, QiCO → QiB, QiBO → QiA

‡QiAO → QiB, QiBO → QiC, QiCO → QiD

## push-pop stack control

The 4-word push-pop stack can be used for nesting up to four levels of program or return (link) addresses. In the load mode, the first (top) word is filled with new data from the output of the full adder, and no push occurs meaning that previous data at that location is lost. However, all other word locations in the push-pop stack remain unchanged. In the push mode, the new word is again entered in the first (top) location; however, previous data residing in the top three words are pushed down one word location and retained at their new locations. The bottom word is written over and lost.

In the pop mode, words in the push-pop stack move up one location on each clock transition. A unique function is provided by the bottom (fourth) register as its content is retained during the pop mode, and after 3 clock transitions, all words in the stack are filled with the operand/address that occupied the bottom register.

The operand/address will remain available indefinitely if stack functions are limited to the pop or hold modes.

The push-pop stack functions are shown in Tables II and III.

TABLE III. PUSH-POP STACK FUNCTIONS

|       | SUNCTION | SEL.      |    | REG.         | REG.     | REG.     | REG.     | INPUT/  |

|-------|----------|-----------|----|--------------|----------|----------|----------|---------|

|       | FUNCTION | <b>S3</b> | S4 | D            | С        | 8        | A        | OUTPUT  |

| BIT 0 | LOAD     | L         | н  | QiD0         | QiC0     | QiB0     | ←<br>Σi  | Σi IN   |

|       |          |           |    | <b>←</b>     | <b>←</b> | +        | <b>←</b> |         |

| BIT 1 | PUSH     | н         | Н  | QiC0         | QiB0     | QiA0     | Σί       | ΣίΙΝ    |

|       |          | 4.        |    | <b>€</b> 0 → | <b>→</b> | <b>→</b> | <b>→</b> |         |

| BIT 2 | POP      | Н         | L  | QiD0         | QiD0     | QiC0     | QiB0     | QiA OUT |

| BIT 3 | HOLD     | L         | L  | QiD0         | QiC0     | QiB0     | QiA0     | QiA OUT |

$\mu$ link operations show previous data location after clock transition.

#### full adder

The four-function full adder is controllable from select inputs S1 and S2 to perform:

A or B incrementation, or decrementation of B

Unconditional jumps or relative offsets

No change

Return to zero or one

Incrementation can be implemented by forcing a carry (high) into the ALU. In this mode either of the following options are possible:

- 1. Increment (A plus zero plus carry)

- 2. Increment B (zero plus B plus carry), or decrement B (all highs at A then A plus B with carry input low and disregard, don't use, carry out)

- 3. Increment the jump or offset (A plus B plus carry)

- 4. Start at zero or one and increment on each clock (select zero plus zero plus carry, then select zero plus B plus carry), or set register to N and decrement B (see 2 above).

- 5. No change (carry input is always active and removal of carry combined with either the ALU or register hold mode will retain the current address).

Unconditional jumps can be implemented by applying and selecting the jump directly from the data inputs to the output register. Offset can be accomplished by summing the output register with the offset magnitude (A plus B) with carry low.

The ALU functions are shown in Table IV.

TABLE IV. ADDRESS CONTROL FUNCTIONS

| INP | UTS | INTERNAL             |

|-----|-----|----------------------|

| S1  | S2  | Σi                   |

| Н   | Н   | O PLUS O PLUS C-in   |

| Н   | L   | O PLUS Bi PLUS C-in  |

| L   | Н   | Ai PLUS 0 PLUS C-in  |

| L   | L   | Ai PLUS Bi PLUS c-in |

#### compound generator functions

As the function-select lines of the register sources, push-pop stack, and adder are independent, compound functions can be selected to occur on the next clock transition.

Subroutine branches and returns can be simplified by saving the return or link addresses in the push-pop stack. This branch-and-save function can be accomplished on the same clock time as follows:

| DATA-IN        | ADDER                | PUSH-POP STACK | REGISTER SOURCE |

|----------------|----------------------|----------------|-----------------|

| Branch address | Zero plus B plus one | Push           | Data-in         |

|                | (S1 = H S2 = I)      | (S3 = S4 = H)  | (S5 = S6 = 1)   |

Up to four branches can be made with the return stored in the 4-word push-pop stack.

# absolute maximum ratings over operating free-air temperature (unless otherwise noted)

| Supply voltage, VCC (see Note 1)               | 7 V            |

|------------------------------------------------|----------------|

| Input voltage                                  | 5.5 V          |

| Off-state output voltage                       | 5.5 V          |

| Operating free-air temperature range: SN54S482 | -55°C to 125°C |

| SN74S482                                       | 0°C to 70°C    |

| Storage temperature range                      | -65°C to 150°C |

NOTE 1. All voltage values are with respect to network ground terminal.

## recommended operating conditions

|                 |                               |                                   | S                                                                                                                                                         | SN54S482 SN74S                    |     | 174548                                                                        | 74\$482         |                         |      |

|-----------------|-------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----|-------------------------------------------------------------------------------|-----------------|-------------------------|------|

|                 |                               |                                   | MIN                                                                                                                                                       | NOM                               | MAX | MIN                                                                           | NOM             | MAX                     | UNIT |

| Vcc             | Supply voltage                |                                   | 4.5                                                                                                                                                       | 5                                 | 5.5 | 4.75                                                                          | 5               | 5.25                    | V    |

| VIH             | High-level input voltage      |                                   | 2                                                                                                                                                         |                                   |     | 2                                                                             |                 |                         | V    |

| VIL             | Low-level input voltage       |                                   |                                                                                                                                                           |                                   | 0.8 |                                                                               |                 | 0.8                     | V    |

|                 | High level common common      | C <sub>out</sub>                  |                                                                                                                                                           |                                   | - 1 |                                                                               |                 | - 1                     | mA   |

| ЮН              | High-level output current     | Any F                             |                                                                                                                                                           |                                   | -2  |                                                                               |                 | 0M MAX<br>5 5.25<br>0.8 | "'A  |

| l               | t any lavel output ourrest    | C <sub>out</sub>                  | AF     -2     -2       It     10     10       If     16     16       I high or low     50     30       I low     15     15       a-in, S5, S6     0     0 | mA                                |     |                                                                               |                 |                         |      |

| IOL             | Low-level output current      | Any F                             |                                                                                                                                                           |                                   | 16  |                                                                               |                 | 16                      | IIIA |

| _               | Pulse duration                | CLK high or low                   | 50                                                                                                                                                        |                                   |     | 30                                                                            |                 |                         | ns   |

| <sup>t</sup> w  | Pulse duration                | CLR low                           | 15                                                                                                                                                        |                                   |     | 15                                                                            |                 |                         | 115  |

|                 |                               | Data-in, S5, S6                   | 0                                                                                                                                                         |                                   |     | 0                                                                             |                 |                         | ns   |

|                 |                               | Data-in via adder to stack        | 35                                                                                                                                                        |                                   |     | 30                                                                            |                 |                         |      |

|                 | Control time before CLV+      | Data-in via adder to output latch | 25                                                                                                                                                        |                                   |     | 20                                                                            |                 |                         |      |

| <sup>t</sup> su | Setup time, before CLK1       | \$1, \$2                          | 40                                                                                                                                                        |                                   |     | 30                                                                            | 0.8 -1 -2 10 16 | 115                     |      |

|                 |                               | S3, S4                            | 20                                                                                                                                                        | 30<br>5 20<br>0 30<br>0 15<br>0 0 |     |                                                                               |                 |                         |      |

|                 |                               | CLR, inactive state               | 0                                                                                                                                                         |                                   |     | 0                                                                             |                 |                         |      |

| t <sub>r</sub>  | CLK input rise time           |                                   | 20                                                                                                                                                        |                                   |     | 25                                                                            |                 |                         | ns   |

|                 |                               | Data-in, S5, S6                   | 30                                                                                                                                                        |                                   |     | 25                                                                            |                 |                         |      |

|                 | Hald diese of the OLKA        | Data-in via adder                 | 15                                                                                                                                                        |                                   |     | 10                                                                            |                 |                         | ns   |

| th              | Hold time, after CLK1         | S1, S2                            | 15                                                                                                                                                        |                                   |     | 2 0.8 0.8 0.8 -1 -1 -2 -2 10 10 10 16 30 15 0 30 20 30 15 0 25 25 10 10 10 20 |                 |                         |      |

|                 |                               | S3, S4                            | 25                                                                                                                                                        |                                   |     | 20                                                                            |                 |                         |      |

| TA              | Operating free-air temperatur | e                                 | - 55                                                                                                                                                      |                                   | 125 | 0                                                                             |                 | 70                      | °C   |

SDLS212 - MARCH 1976 - REVISED OCTOBER 1980

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                | PARAMETER               | TECT COM                     | DITIONO †                | S   | N54S4            | B2    | SA   |                  |       |          |  |

|----------------|-------------------------|------------------------------|--------------------------|-----|------------------|-------|------|------------------|-------|----------|--|

|                |                         | TEST CONDITIONS <sup>†</sup> |                          |     | TYP <sup>‡</sup> | MAX   | MIN  | TYP <sup>‡</sup> | MAX   | UNIT     |  |

| VIK            |                         | V <sub>CC</sub> = MIN,       | I <sub>L</sub> = -18 mA  |     |                  | -1.2  |      |                  | - 1.2 | V        |  |

| Vон            | C <sub>out</sub>        | V <sub>CC</sub> = MIN,       | IOH = -1 mA              | 2.5 | 3.4              |       | 2.7  | 3.4              |       |          |  |

| νон            | Any F                   | V <sub>CC</sub> = MIN,       | I <sub>OH</sub> = -2 mA  | 2.5 | 3.4              |       | 2.7  | 3.4              |       | V        |  |

| VOL            | Cout                    | V <sub>CC</sub> = MIN,       | IOL = 10 mA              |     |                  | 0.5   |      |                  | 0.5   |          |  |

| VOL            | Any F                   | V <sub>CC</sub> = MIN,       | I <sub>OL</sub> = 16 mA  |     |                  | 0.5   |      |                  | 0.5   | V        |  |

| l <sub>l</sub> |                         | V <sub>CC</sub> = MIN,       | V <sub>I</sub> = 5.5 V   |     |                  | 1     |      |                  | 1     | mA       |  |

| ΉΗ             | S1, S2, C <sub>in</sub> | V <sub>CC</sub> = MAX,       | V <sub>I</sub> = 2.7 V   |     |                  | 50    |      |                  | 50    | μΑ       |  |

|                | S3, S4, S5, S6, CLK     |                              |                          |     | -                | 0.1   |      |                  | 0.1   |          |  |

|                | CLR                     |                              |                          |     |                  | 0.25  |      |                  | 0.25  |          |  |

|                | Any A                   |                              |                          |     | ,                | 0.15  |      |                  | 0.15  | <u> </u> |  |

|                | S1, S2                  |                              | , V <sub>I</sub> = 0.5 V |     |                  | - 1   |      |                  | -1    |          |  |

|                | C <sub>in</sub>         |                              |                          |     |                  | -0.8  |      |                  | -0.8  | }        |  |

| f              | S3, S4                  | V 444V                       |                          |     |                  | -1.2  |      | ·                | -1.2  |          |  |

| Iμ             | Any A, S5, S6           | VCC = MAX,                   |                          |     |                  | - 2   |      |                  | - 2   | mA       |  |

|                | CLR                     |                              |                          |     |                  | -4    |      |                  | -4    | ĺ        |  |

|                | CLK                     |                              |                          |     |                  | - 2.8 |      |                  | - 2.8 |          |  |

| los§           |                         | V <sub>CC</sub> = MAX        |                          | -40 |                  | -110  | - 40 |                  | -110  | mA       |  |

| Icc            |                         | V <sub>CC</sub> = MAX        |                          |     | 90               | 130   |      | 90               | 140   | mA       |  |

<sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.  $^{\ddagger}$ All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C.

## switching characteristics (see Note 1)

| PARAMETER        | METER FROM TO (INPUT) (OUTPUT) |                  | $V_{CC}$ = MIN to MAX $C_L$ = 15 pF $R_L$ = 280 $\Omega$ $T_A$ = MIN to MAX |          |          |     |    |  |  |

|------------------|--------------------------------|------------------|-----------------------------------------------------------------------------|----------|----------|-----|----|--|--|

|                  |                                |                  | SN54S4                                                                      | SN54S482 |          |     | 7  |  |  |

|                  |                                |                  | MIN TYP‡                                                                    | MAX      | MIN TYP‡ | MAX | 1  |  |  |

| tpLH             | CLK                            | Any F            | 12                                                                          | 30       | 12       | 25  |    |  |  |

| <sup>t</sup> PHL | CLK                            | Any F            | 15                                                                          | 30       | 15       | 25  | ns |  |  |

| tPHL             | CLR                            | Any F            | 12                                                                          | 25       | 12       | 20  | ns |  |  |

| <sup>t</sup> PLH | C.                             | C                | 12                                                                          | 22       | 12       | 18  | ns |  |  |

| tPHL             | C <sub>in</sub>                | C <sub>out</sub> | 10                                                                          | 22       | 10       | 18  |    |  |  |

| <sup>t</sup> PLH | Any A                          | C .              | 17                                                                          | 30       | 17       | 25  | †  |  |  |

| <sup>t</sup> PHL | 507.5                          | C <sub>out</sub> | 12                                                                          | 30       | 12       | 23  | ns |  |  |

$^{\ddagger}All$  typical values are at VCC = 5 V, TA = 25 °C. NOTE 1: See General Information Section for load circuit and voltage waveforms.

<sup>§</sup>Not more than one output should be shorted at a time.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated