ONE AL COTO

SDLS195 - MARCH 1985 - REVISED MARCH 1988

LOD MUDACKAOE

### 'LS673

- 16-Bit Serial-In, Serial-Out Shift Register with 16-Bit Parallel-Out Storage Register

- Performs Serial-to-Parallel Conversion

### 'LS674

- 16-Bit Parallel-In, Serial-Out Shift Register

- Performs Parallel-to-Serial Conversion

### description

### SN54LS673, SN74LS673

The 'LS673 is a 16-bit shift register and a 16-bit storage register in a single 24-pin package. A three-state input/output (SER/Q15) port to the shift register allows serial entry and/or reading of data. The storage register is connected in a parallel data loop with the shift register and may be asynchronously cleared by taking the store-clear input low. The storage register may be parallel loaded with shift-register data to provide shift-register status via the parallel outputs. The shift register can be parallel loaded with the storage-register data upon command.

A high logic level at the chip-level  $(\overline{CS})$  input disables both the shift-register clock and the storage register clock and places SER/Q15 in the high-impedance state. The store-clear function is not disabled by the chip select.

Caution must be exercised to prevent false clocking of either the shift register or the storage register via the chip-select input. The shift clock should be low during the low-to-high transition of chip select and the store clock should be low during the high-to-low transition of chip select.

#### SN54LS674, SN74LS674

The 'LS674 is a 16-bit parallel-in, serial-out shift register. A three-state input/output (SER/Q15) port provides access for entering a serial data or reading the shift-register word in a recirculating loop.

The device has four basic modes of operation:

- 1) Hold (do nothing)

- 2) Write (serially via input/output)

- 3) Read (serially)

- 4) Load (parallel via data inputs)

Low-to-high-level changes at the chip select input should be made only when the clock input is low to prevent false clocking.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

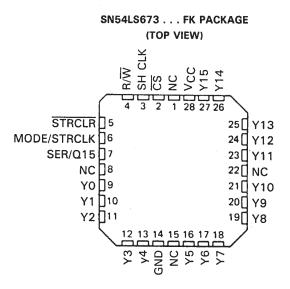

| SN54LS673 J OR W PACKA<br>SN74LS673 DW OR N PACKA |  |

|---------------------------------------------------|--|

| (TOP VIEW)                                        |  |

|                                                   |  |

| SH CLK [      | 2   | 23 Y15   |

|---------------|-----|----------|

| R/W [         | 3   | 22 Y14   |

| STRCLR [      | _]4 | 21 Y13   |

| MODE/STRCLK [ | 5   | 20 Y12   |

| SER/Q15 [     | 6   | 19 Y11   |

| Y0 [          | 7   | 18 Y10   |

| Y1 [          | 8   | 17 🛛 Y9  |

| Y2 [          | _]9 | 16 🗌 Y8  |

| Y3 [          | 10  | 15 🗍 Y7  |

| Y4 [          | 111 | 14 🗋 Y6  |

| GND [         | 12  | 13 🗋 Y 5 |

NC-No internal connection

SDLS195 - MARCH 1985 - REVISED MARCH 1988

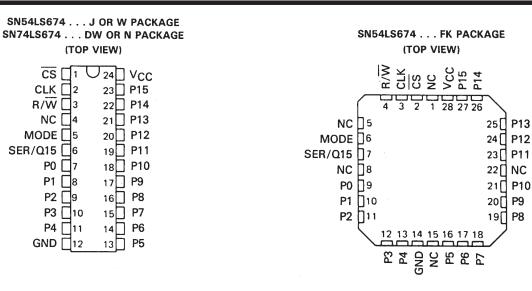

CLK 2

MODE 5

SER/Q15 6

NC 14

P0 7

P1 [8

P2 9

P3 [10

P4 [11

GND [12

'LS673 **FUNCTION TABLE**

|            | INPUTS SER/ |        |        |                 |      |       | SHIFT REGIS                | STORAGE<br>REGISTER        |                  |               |               |

|------------|-------------|--------|--------|-----------------|------|-------|----------------------------|----------------------------|------------------|---------------|---------------|

| <b>C</b> S | R/W         | SH CLK | STRCLR | MODE/<br>STRCLK | Q15  | SHIFT | READ FROM<br>SERIAL OUTPUT | WRITE INTO<br>SERIAL INPUT | PARALLEL<br>LOAD | FUNC<br>CLEAR | FIONS<br>LOAD |

| Н          | Х           | Х      | Х      | х               | Z    | NO    | NO                         | NO                         | NO               |               | NO            |

| Х          | Х           | Х      | L      | Х               |      |       |                            |                            |                  | YES           |               |

| L          | L           | Ļ      | Х      | Х               | Z    | YES   | NO                         | YES                        | NO               |               |               |

| L          | н           | х      | Х      | Х               | Q15  |       | YES                        | NÖ                         |                  |               | NO            |

| L          | н           | Ļ      | Х      | L               | Q14n | YES   | YES                        | NO                         | NO               |               | NO            |

| L          | н           | Ļ      | L      | н               | L    | NO    | YES                        |                            | YES              | YES           | NO            |

| L          | н           | Ļ      | Н      | Н               | Y15n | NO    | YES                        |                            | YES              | NO            | NO            |

| L          | L           | Х      | Н      | Ť               | Z    |       | NO                         |                            | NO               | NO            | YES           |

**'LS674 FUNCTION TABLE**

|    |     | INPUTS |     |      |                               |

|----|-----|--------|-----|------|-------------------------------|

| CS | R/W | MODE   | CLK | Q15  | OPERATION                     |

| н  | х   | x      | х   | Z    | Do nothing                    |

| L  | L   | х      | 4   | z    | Shift and write (serial load) |

| L  | н   | L      | ŧ   | Q14n | Shift and read                |

| L  | н   | н      | Ļ   | P15  | Parallel load                 |

H = high level (steady state)

L = low level (steady state)

1 = transition from low to high level

↓ = transition from high to low level

X = irrelevant (any input including transitions)

Z = high impedance, input mode

Q14n = content of 14th bit of the shift register before the most recent 4 transition of the clock.

Q15 = present content of 15th bit of the shift register Y15n = content of the 15th bit of the storage register

before the most recent \$ transition of the clock. P15 = level of input P15

SDLS195 - MARCH 1985 - REVISED MARCH 1988

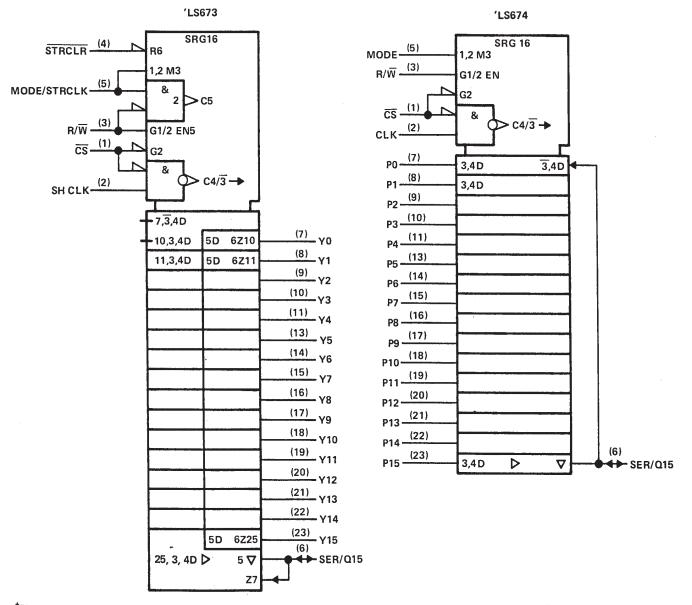

logic symbols<sup>†</sup>

SDLS195 – MARCH 1985 – REVISED MARCH 1988

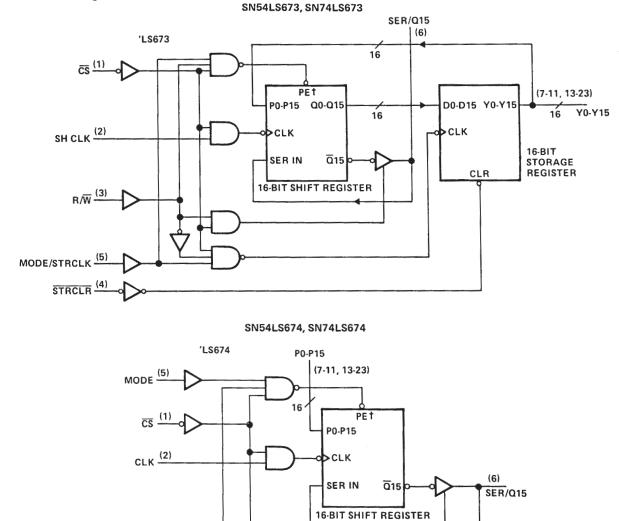

## functional block diagrams

<sup>†</sup>When PE is active, data is synchronously parallel loaded into the shift registers from the 16 P inputs and no shifting takes place. Pin numbers shown are for DW, J, N, and W packages.

R/W (3)

SDLS195 - MARCH 1985 - REVISED MARCH 1988

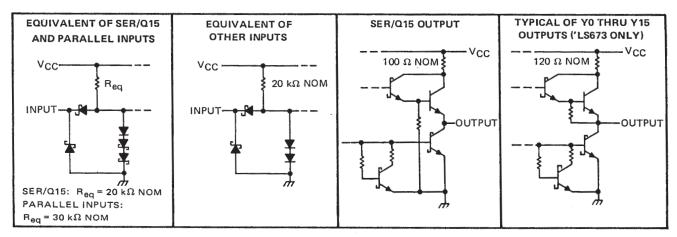

## schematics of inputs and outputs

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Input voltage: SER/      | Q15                |                                         | <br>5.5 V          |

|--------------------------|--------------------|-----------------------------------------|--------------------|

| All ot                   | hers               |                                         | <br>               |

| Off-state output voltage | ge                 |                                         | <br>5.5 V          |

| Operating free-air tem   | perature range: SN | 54LS673, SN54LS674                      | <br>–55°C to 125°C |

|                          | ` SN               | 74LS673, SN74LS674                      | <br>               |

| Storage temperature ra   | ange               | • • • • • • • • • • • • • • • • • • • • | <br>–65°C to 150°C |

NOTE 1. Voltage values are with respect to network ground terminal.

#### recommended operating conditions

|                       |                                |                                          |        |     | SN54LS | *    | 5    | SN74LS' |      | UNIT |

|-----------------------|--------------------------------|------------------------------------------|--------|-----|--------|------|------|---------|------|------|

|                       |                                |                                          |        | MIN | NOM    | MAX  | MIN  | NOM     | MAX  | UNIT |

| V <sub>CC</sub>       | Supply voltage                 |                                          |        | 4.5 | 5      | 5.5  | 4.75 | 5       | 5.25 | V    |

| lou                   | High-level output current      | SER/Q15                                  |        |     |        | - 1  |      |         | -2.6 | mA   |

| IOH                   | nigh-level output current      | Y0 thru Y15                              |        |     |        | -0.4 |      |         | -0.4 |      |

| Lou Low               | Low-level output current       | SER/Q15                                  |        |     |        | 12   |      |         | 24   | mA   |

| UL                    | IOL Low-level output current   |                                          |        |     |        | 4    |      |         | 8    |      |

| fclock                | Clock frequency                |                                          |        |     |        | 20   | 0    |         | 20   | MHz  |

| <sup>t</sup> w(clock) | Width of clock input pulse     |                                          |        | 20  |        |      | 20   |         |      | ns   |

| <sup>t</sup> w(clear) | Width of clear input pulse     |                                          |        | 20  |        |      | 20   |         |      | ns   |

|                       |                                | SER/Q15                                  |        | 20  |        |      | 20   |         |      |      |

|                       | Setup time                     | PO thru P15                              | 20     |     |        | 20   |      |         |      |      |

| +                     |                                | Mode                                     | 35     |     |        | 35   |      |         | ns   |      |

| t <sub>su</sub>       | Setup time                     | R/W, CS                                  | 35     |     |        | 35   |      |         | 113  |      |

|                       |                                | SH CLK ↓ to Mode/STR CLK ↑<br>See Note 2 |        | 25  |        |      | 25   |         |      | 1    |

|                       |                                | SER/Q15                                  |        | 0   |        |      | 0    |         |      |      |

| <b>.</b>              | Hold time                      | P0 thru P15                              | 'LS673 | 0   |        |      | 0    |         |      | ns   |

| th                    | noid diffe                     |                                          | 'LS674 | 5.0 |        |      | 5.0  |         |      | ] "" |

|                       |                                | Mode                                     |        | 0   |        |      | 0    |         |      | 1    |

| TA                    | Operating free-air temperature |                                          |        |     |        | 125  | 0    |         | 70   | °C   |

NOTE 2: This setup time ensures the storage register will see stable data from the shift register.

#### SDLS195 – MARCH 1985 – REVISED MARCH 1988

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                              | PARAMETER                     |                        | TEGT CON                              |                        |      | SN54LS |       |      | S'   |       |    |

|------------------------------|-------------------------------|------------------------|---------------------------------------|------------------------|------|--------|-------|------|------|-------|----|

|                              | PARAMETER                     |                        | TEST CON                              | MIN                    | түр‡ | MAX    | MIN   | TYP‡ | MAX  | UNIT  |    |

| VIH                          | High-level input voltage      |                        |                                       |                        | 2    |        |       | 2    |      |       | V  |

| VIL                          | Low-level input voltage       |                        |                                       |                        |      |        | 0.7   |      |      | 0.8   | V  |

| Vik                          | Input clamp voltage           |                        | V <sub>CC</sub> = MIN,                | lj =18 mA              |      |        | -1.5  |      |      | -1.5  | V  |

| ∨он                          | High-level output voltage     | SER/Q15                | V <sub>CC</sub> = MIN,                | V <sub>IH</sub> = 2 V, | 2.4  | 3.2    |       | 2.4  | 3.1  |       | v  |

| Ч                            |                               | Y0 thru Y15¶           | VIL = VILmax,                         | IOH = MAX              | 2.5  | 3.4    |       | 2.7  | 3.4  |       | Ň  |

| VOL Low-level output voltage | SER/Q15                       | V <sub>CC</sub> = MIN, | 1 <sub>OL</sub> = 12 mA               |                        | 0.25 | 0.4    |       | 0.25 | 0.4  |       |    |

|                              |                               | $V_{IH} = 2 V$ ,       | IOL = 24 mA                           |                        |      |        |       | 0.35 | 0.5  |       |    |

|                              | Y0 thru Y15¶                  | VIL = VILmax           | IOL = 4 mA                            |                        | 0.25 | 0.4    |       | 0.25 | 0.4  | Ì     |    |

|                              |                               |                        | VIE VIEINAX                           | I <sub>OL</sub> = 8 mA |      |        |       |      | 0.35 | 0.5   |    |

| IOZH                         | Off-state output current,     | SER/Q15                | V <sub>CC</sub> = MAX,                | $V_{IH} = 2 V,$        |      |        | 40    |      |      | 40    | μA |

| -021                         | high-level voltage applied    | 0211/210               | VIL ≈ VILmax,                         | V <sub>O</sub> = 2.7 V |      |        | 40    |      |      |       | μ. |

| IOZL                         | Off-state output current,     | SER/Q15                | $V_{CC} = MAX,$                       | VIH = 2 V,             |      | - 0.4  |       |      | 0    | 0.4   |    |

| 026                          | low-level voltage applied     | JEN/Q15                | VIL = VILmax,                         | V <sub>O</sub> = 0.4 V |      |        | - 0.4 |      |      | - 0.4 | mA |

| lj –                         | Input current at maximum      | SER/Q15                | V <sub>CC</sub> = MAX                 | V <sub>1</sub> = 5.5 V |      |        | 0.1   |      |      | 0.1   |    |

| ''                           | input voltage                 | Others                 |                                       | V  = 7 V               |      |        | 0.1   |      |      | 0.1   | mA |

| ЧН                           | High-level input current      | SER/Q15                | V <sub>CC</sub> = MAX,                | Vi = 2.7 V             |      |        | 40    |      |      | 40    | μA |

| - 111                        |                               | Others                 | · · · · · · · · · · · · · · · · · · · |                        |      |        | 20    |      |      | 20    | μΑ |

| ΊL                           | Low-level input current       |                        | V <sub>CC</sub> = MAX,                | VI = 0.4 V             |      |        | -0.4  |      |      | -0.4  | mA |

| los                          | Short-circuit output current§ | SER/Q15                | V <sub>CC</sub> = MAX                 |                        | -30  |        | -130  | -30  |      | -130  | mA |

|                              |                               | Y0 thru Y15¶           |                                       |                        | -20  |        | -100  | -20  |      | -100  |    |

| ICC                          | Supply current                | 'LS673                 | V <sub>CC</sub> = MAX                 |                        |      | 50     | 80    | L    | 52   | 80    | mA |

|                              |                               | 'LS674                 |                                       |                        |      | 25     | 40    |      | 25   | 40    |    |

<sup>†</sup>For conditions shown as MIN or MAX use the appropriate value specified under recommended operating conditions.

<sup>‡</sup>All typical values are at  $V_{CC} = 5 V$ ,  $T_A = 25^{\circ}C$ .

Not more than one output should be shorted at a time, and duration of the short circuit should not exceed one second. I' LS673 only.

## switching characteristics, $V_{CC}$ = 5 V, $T_A$ = 25°C, see note 2

| PARAMETER        | 'LS673         |                | 'LS      | 674     | TEST CONDITIONS                                | -       | TVD     | MAX     | 1.15.11.77 |     |         |                        |  |    |    |  |

|------------------|----------------|----------------|----------|---------|------------------------------------------------|---------|---------|---------|------------|-----|---------|------------------------|--|----|----|--|

| FARAMETER        | FROM           | то             | FROM     | то      | TEST CONDITIONS                                | MIN     | түр     | MAX     | UNIT       |     |         |                        |  |    |    |  |

| f <sub>max</sub> | SHCLK          | SER/Q15        | CLK      | SER/Q15 | R <sub>L</sub> = 667 Ω, C <sub>L</sub> = 45 pF | 20      | 28      |         | MHz        |     |         |                        |  |    |    |  |

| <sup>t</sup> PHL | STRCLR         | Y0 thru Y15    |          |         |                                                |         | 25      | 40      |            |     |         |                        |  |    |    |  |

| <b>TPLH</b>      | MODE/          | Y0 thru Y15    |          |         | $R_L = 2 k\Omega, C_L = 15 pF$                 |         | 28      | 45      | ns         |     |         |                        |  |    |    |  |

| <sup>t</sup> PHL | STRCLK         | 10 111 115     |          |         |                                                |         | 30      | 45      | 1          |     |         |                        |  |    |    |  |

| tPLH             | SH CLK SER/Q15 | SER/O15        | SER/015  | SER/Q15 | SEB/015                                        | SER/015 | SER/015 | SEB/015 | K SEB/015  | CLK | SER/Q15 | RL = 667 Ω, CL = 45 pF |  | 21 | 33 |  |

| <sup>t</sup> PHL | SHOEK          | oen/aro        | CER      | 311/013 | n_=007 32, 0L = 45 pr                          |         | 26      | 40      | ns         |     |         |                        |  |    |    |  |

| <sup>t</sup> PZH | CS, R/W        | SER/Q15        | CS, R/₩  | SER/Q15 | R <sub>L</sub> = 667 Ω, C <sub>L</sub> = 45 pF |         | 30      | 45      | ns         |     |         |                        |  |    |    |  |

| <sup>t</sup> PZL | 00,11/1        | SEN/QIS        | 03,11/1  | SEN/QT5 | NL - 007 32, CL - 45 pr                        |         | 30      | 45      | 1 115      |     |         |                        |  |    |    |  |

| <sup>t</sup> PHZ | ĊŠ, R/₩        | SER/Q15        | ĊŠ, R/₩  | SER/Q15 | RL = 667 Ω, CL = 5 pF                          |         | 25      | 40      | -          |     |         |                        |  |    |    |  |

| tPLZ             | 00,11/1        | 5, H/W 5ER/Q15 | 03, 11/1 | 3ER/Q15 | 11 - 007 32, C[ - 5 pF                         |         | 25      | 40      | ns         |     |         |                        |  |    |    |  |

NOTE 2: Load circuits and voltage waveforms are shown in Section 1.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated