# MM54C922/MM74C922 16-Key Encoder MM54C923/MM74C923 20-Key Encoder

### **General Description**

These CMOS key encoders provide all the necessary logic to fully encode an array of SPST switches. The keyboard scan can be implemented by either an external clock or external capacitor. These encoders also have on-chip pull-up devices which permit switches with up to  $50~\mathrm{k}\Omega$  on resistance to be used. No diodes in the switch array are needed to eliminate ghost switches. The internal debounce circuit needs only a single external capacitor and can be defeated by omitting the capacitor. A Data Available output goes to a high level when a valid keyboard entry has been made. The Data Available output returns to a low level when the entered key is released, even if another key is depressed. The Data Available will return high to indicate acceptance of the new key after a normal debounce period; this two-key rollover is provided between any two switches.

An internal register remembers the last key pressed even after the key is released. The TRI-STATE® outputs provide for easy expansion and bus operation and are LPTTL compatible.

### **Features**

- 50 k $\Omega$  maximum switch on resistance

- On or off chip clock

- On-chip row pull-up devices

- 2 key roll-over

- Keybounce elimination with single capacitor

- Last key register at outputs

- TRI-STATE outpust LPTTL compatible

- Wide supply range

3V to 15V

MM54C922/MM74C922 16-Key Encoder, MM54C923/MM74C923 20-Key Encodei

#### ■ Low power consumption

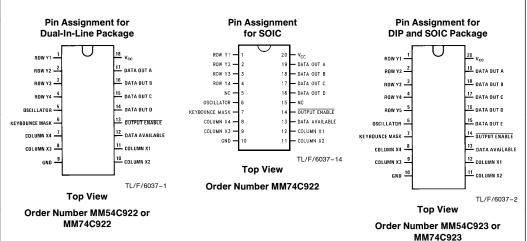

# **Connection Diagrams**

TRI-STATE® is a registered trademark of National Semiconductor Corporation

### **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Voltage at Any Pin  $V_{\mbox{\footnotesize CC}} - \mbox{\footnotesize 0.3V}$  to  $V_{\mbox{\footnotesize CC}} + \mbox{\footnotesize 0.3V}$ Operating Temperature Range MM54C922, MM54C923

-55°C to +125°C -40°C to +85°C MM74C922, MM74C923

Storage Temperature Range  $-65^{\circ}\text{C}$  to  $+150^{\circ}\text{C}$

Power Dissipation (PD) Dual-In-Line

700 mW Small Outline 500 mW Operating V<sub>CC</sub> Range 3V to 15V  $V_{CC}$ 18V

260°C

Lead Temperature

(Soldering, 10 seconds)

DC Electrical Characteristics Min/Max limits apply across temperature range unless otherwise specified

| Symbol              | Parameter                                               | Conditions                                                                                                                                                                                                                    | Min                                            | Тур                | Max                | Units                      |

|---------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------------------|--------------------|----------------------------|

| CMOS TO             | CMOS                                                    |                                                                                                                                                                                                                               |                                                |                    |                    |                            |

| $V_{T+}$            | Positive-Going Threshold Voltage at Osc and KBM Inputs  | $\begin{array}{c} \text{V}_{CC} = 5\text{V, I}_{\text{IN}} \geq 0.7 \text{ mA} \\ \text{V}_{CC} = 10\text{V, I}_{\text{IN}} \geq 1.4 \text{ mA} \\ \text{V}_{CC} = 15\text{V, I}_{\text{IN}} \geq 2.1 \text{ mA} \end{array}$ | 3.0<br>6.0<br>9.0                              | 3.6<br>6.8<br>10   | 4.3<br>8.6<br>12.9 | V<br>V<br>V                |

| $V_{T-}$            | Negative-Going Threshold Voltage at Osc and KBM Inputs  | $\begin{array}{l} \text{V}_{CC} = 5\text{V, I}_{IN} \geq 0.7 \text{ mA} \\ \text{V}_{CC} = 10\text{V, I}_{IN} \geq 1.4 \text{ mA} \\ \text{V}_{CC} = 15\text{V, I}_{IN} \geq 2.1 \text{ mA} \end{array}$                      | 0.7<br>1.4<br>2.1                              | 1.4<br>3.2<br>5    | 2.0<br>4.0<br>6.0  | > > >                      |

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage,<br>Except Osc and KBM Inputs | $V_{CC} = 5V$ $V_{CC} = 10V$ $V_{CC} = 15V$                                                                                                                                                                                   | 3.5<br>8.0<br>12.5                             | 4.5<br>9<br>13.5   |                    | V<br>V<br>V                |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage,<br>Except Osc and KBM Inputs | V <sub>CC</sub> = 5V<br>V <sub>CC</sub> = 10V<br>V <sub>CC</sub> = 15V                                                                                                                                                        |                                                | 0.5<br>1<br>1.5    | 1.5<br>2<br>2.5    | V<br>V<br>V                |

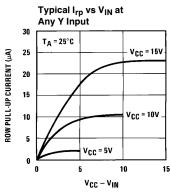

| I <sub>rp</sub>     | Row Pull-Up Current at Y1, Y2,<br>Y3, Y4 and Y5 Inputs  | $V_{CC} = 5V, V_{IN} = 0.1 V_{CC}$<br>$V_{CC} = 10V$<br>$V_{CC} = 15V$                                                                                                                                                        |                                                | -2<br>-10<br>-22   | -5<br>-20<br>-45   | μΑ<br>μΑ<br>μΑ             |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage                              | $V_{CC} = 5V, I_{O} = -10 \mu A$ $V_{CC} = 10V, I_{O} = -10 \mu A$ $V_{CC} = 15V, I_{O} = -10 \mu A$                                                                                                                          | 4.5<br>9<br>13.5                               |                    |                    | V<br>V<br>V                |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage                              | $V_{CC} = 5V, I_O = 10 \mu A$ $V_{CC} = 10V, I_O = 10 \mu A$ $V_{CC} = 15V, I_O = 10 \mu A$                                                                                                                                   |                                                |                    | 0.5<br>1<br>1.5    | V<br>V<br>V                |

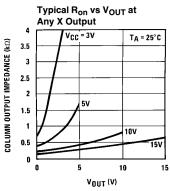

| R <sub>on</sub>     | Column "ON" Resistance at X1, X2, X3 and X4 Outputs     | $V_{CC} = 5V, V_{O} = 0.5V$<br>$V_{CC} = 10V, V_{O} = 1V$<br>$V_{CC} = 15V, V_{O} = 1.5V$                                                                                                                                     |                                                | 500<br>300<br>200  | 1400<br>700<br>500 | $\Omega$ $\Omega$ $\Omega$ |

| Icc                 | Supply Current<br>Osc at 0V, (one Y low)                | V <sub>CC</sub> = 5V<br>V <sub>CC</sub> = 10V<br>V <sub>CC</sub> = 15V                                                                                                                                                        |                                                | 0.55<br>1.1<br>1.7 | 1.1<br>1.9<br>2.6  | mA<br>mA<br>mA             |

| I <sub>IN(1)</sub>  | Logical "1" Input Current at Output Enable              | $V_{CC} = 15V, V_{IN} = 15V$                                                                                                                                                                                                  |                                                | 0.005              | 1.0                | μΑ                         |

| I <sub>IN(0)</sub>  | Logical "0" Input Current at Output Enable              | $V_{CC} = 15V, V_{IN} = 0V$                                                                                                                                                                                                   | -1.0                                           | -0.005             |                    | μΑ                         |

| CMOS/LF             | PTTL INTERFACE                                          |                                                                                                                                                                                                                               |                                                |                    |                    |                            |

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage,<br>Except Osc and KBM Inputs | 54C, V <sub>CC</sub> = 4.5V<br>74C, V <sub>CC</sub> = 4.75V                                                                                                                                                                   | V <sub>CC</sub> - 1.5<br>V <sub>CC</sub> - 1.5 |                    |                    | V<br>V                     |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage,<br>Except Osc and KBM Inputs | 54C, V <sub>CC</sub> = 4.5V<br>74C, V <sub>CC</sub> = 4.75V                                                                                                                                                                   |                                                |                    | 0.8<br>0.8         | V<br>V                     |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage                              | 54C, $V_{CC} = 4.5V$<br>$I_{O} = -360 \mu\text{A}$<br>74C, $V_{CC} = 4.75V$<br>$I_{O} = -360 \mu\text{A}$                                                                                                                     | 2.4<br>2.4                                     |                    |                    | V<br>V                     |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage                              | $54C, V_{CC} = 4.5V$ $I_{O} = -360 \mu A$                                                                                                                                                                                     |                                                |                    | 0.4                | V                          |

| N-4- d. ((A)-       | solute Maximum Ratings" are those values heyong         | 74C, $V_{CC} = 4.75V$ $I_{O} = -360 \mu A$                                                                                                                                                                                    |                                                |                    | 0.4                | V                          |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Temperature Range" they are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

### **DC Electrical Characteristics**

Min/Max limits apply across temperature range unless otherwise specified (Continued)

| Symbol                                                                               | Parameter                          | Conditions                                                | Min          | Тур  | Max | Units |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------|------------------------------------|-----------------------------------------------------------|--------------|------|-----|-------|--|--|--|--|--|--|--|--|

| OUTPUT DRIVE (See 54C/74C Family Characteristics Data Sheet) (Short Circuit Current) |                                    |                                                           |              |      |     |       |  |  |  |  |  |  |  |  |

| ISOURCE                                                                              | Output Source Current (P-Channel)  | $V_{CC} = 5V$ , $V_{OUT} = 0V$ , $T_A = 25^{\circ}C$      | <b>−1.75</b> | -3.3 |     | mA    |  |  |  |  |  |  |  |  |

| ISOURCE                                                                              | Output Source Current (P-Channel)  | $V_{CC} = 10V, V_{OUT} = 0V, T_A = 25^{\circ}C$           | -8           | -15  |     | mA    |  |  |  |  |  |  |  |  |

| ISINK                                                                                | Output Sink Current<br>(N-Channel) | $V_{CC} = 5V$ , $V_{OUT} = V_{CC}$ , $T_A = 25^{\circ}C$  | 1.75         | 3.6  |     | mA    |  |  |  |  |  |  |  |  |

| I <sub>SINK</sub>                                                                    | Output Sink Current<br>(N-Channel) | $V_{CC} = 10V$ , $V_{OUT} = V_{CC}$ , $T_A = 25^{\circ}C$ | 8            | 16   |     | mA    |  |  |  |  |  |  |  |  |

# AC Electrical Characteristics\* $T_A = 25^{\circ}C, C_L = 50 \text{ pF}, \text{ unless otherwise noted}$

| Symbol                              | Parameter                                                                              | Conditions                                                                                                                                                                                                            | Min | Тур             | Max               | Units          |  |

|-------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|-------------------|----------------|--|

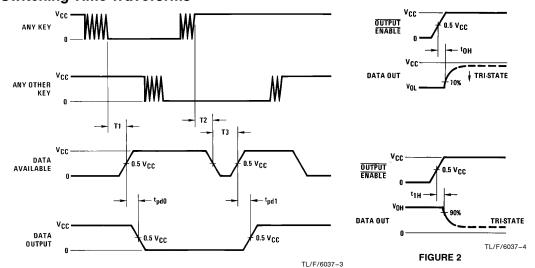

| t <sub>pd0</sub> , t <sub>pd1</sub> | Propagation Delay Time to<br>Logical "0" or Logical "1"<br>from D.A.                   | C <sub>L</sub> = 50 pF (Figure 1)<br>V <sub>CC</sub> = 5V<br>V <sub>CC</sub> = 10V<br>V <sub>CC</sub> = 15V                                                                                                           |     | 60<br>35<br>25  | 150<br>80<br>60   | ns<br>ns<br>ns |  |

| t <sub>0H</sub> , t <sub>1H</sub>   | Propagation Delay Time from<br>Logical "0" or Logical "1"<br>into High Impedance State | R <sub>L</sub> = 10k, C <sub>L</sub> = 10 pF (Figure 2)<br>V <sub>CC</sub> = 5V, R <sub>L</sub> = 10k<br>V <sub>CC</sub> = 10V, C <sub>L</sub> = 10 pF<br>V <sub>CC</sub> = 15V                                       |     | 80<br>65<br>50  | 200<br>150<br>110 | ns<br>ns<br>ns |  |

| t <sub>H0</sub> , t <sub>H1</sub>   | Propagation Delay Time from<br>High Impedance State to a<br>Logical "0" or Logical "1" | $\begin{aligned} & R_L = 10 \text{k, } C_L = 50 \text{ pF } \textit{(Figure 2)} \\ & V_{CC} = 5 \text{V, } R_L = 10 \text{k} \\ & V_{CC} = 10 \text{V, } C_L = 50 \text{ pF} \\ & V_{CC} = 15 \text{V} \end{aligned}$ |     | 100<br>55<br>40 | 250<br>125<br>90  | ns<br>ns<br>ns |  |

| C <sub>IN</sub>                     | Input Capacitance                                                                      | Any Input (Note 2)                                                                                                                                                                                                    |     | 5               | 7.5               | pF             |  |

| C <sub>OUT</sub>                    | TRI-STATE Output Capacitance                                                           | Any Output (Note 2)                                                                                                                                                                                                   |     | 10              |                   | pF             |  |

<sup>\*</sup>AC Parameters are guaranteed by DC correlated testing.

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Temperature Range" they are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

Note 2: Capacitance is guaranteed by periodic testing.

# **Switching Time Waveforms**

T1  $\approx$  T2  $\approx$  RC, T3  $\approx$  0.7 RC, where R  $\approx$  10k and C is external capacitor at KBM input.

FIGURE 1

# **Truth Table**

| Swi  | tch  | 0     | 1     | 2     | 3     | 4     | 5     | 6     | 7     | 8     | 9     | 10    | 11    | 12    | 13    | 14    | 15    | 16     | 17     | 18     | 19     |

|------|------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------|--------|--------|--------|

| Posi | tion | Y1,X1 | Y1,X2 | Y1,X3 | Y1,X4 | Y2,X1 | Y2,X2 | Y2,X3 | Y2,X4 | Y3,X1 | Y3,X2 | Y3,X3 | Y3,X4 | Y4,X1 | Y4,X2 | Y4,X3 | Y4,X4 | Y5*,X1 | Y5*,X2 | Y5*,X3 | Y5*,X4 |

| D    |      |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |        |        |        |        |

| Α    | Α    | 0     | 1     | 0     | 1     | 0     | 1     | 0     | 1     | 0     | 1     | 0     | 1     | 0     | 1     | 0     | 1     | 0      | 1      | 0      | 1      |

| Т    | В    | 0     | 0     | 1     | 1     | 0     | 0     | 1     | 1     | 0     | 0     | 1     | 1     | 0     | 0     | 1     | 1     | 0      | 0      | 1      | 1      |

| Α    | С    | 0     | 0     | 0     | 0     | 1     | 1     | 1     | 1     | 0     | 0     | 0     | 0     | 1     | 1     | 1     | 1     | 0      | 0      | 0      | 0      |

| 0    | D    | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 0      | 0      | 0      | 0      |

| U    | E*   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1      | 1      | 1      | 1      |

| Т    |      | 1     |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |        |        |        |        |

<sup>\*</sup>Omit for MM54C922/MM74C922

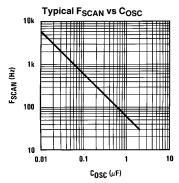

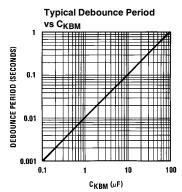

# **Typical Performance Characteristics**

TL/F/6037-6

TL/F/6037-7

TL/F/6037-8

TL/F/6037-9

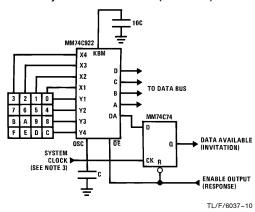

### **Typical Applications**

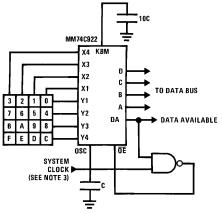

Synchronous Handshake (MM74C922)

### Synchronous Data Entry Onto Bus (MM74C922)

TL/F/6037-11

Outputs are enabled when valid entry is made and go into TRI-STATE when key is released.

Note 3: The keyboard may be synchronously scanned by omitting the capacitor at osc. and driving osc. directly if the system clock rate is lower than 10 kHz.

### Typical Applications (Continued)

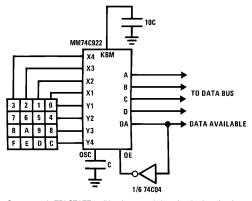

#### Asynchronous Data Entry Onto Bus (MM74C922)

TL/F/6037-12

Outputs are in TRI-STATE until key is pressed, then data is placed on bus. When key is released, outputs return to TRI-STATE.

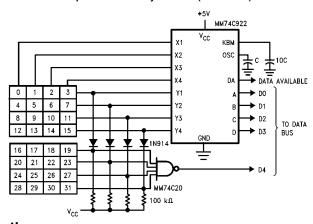

### Expansion to 32 Key Encoder (MM74C922)

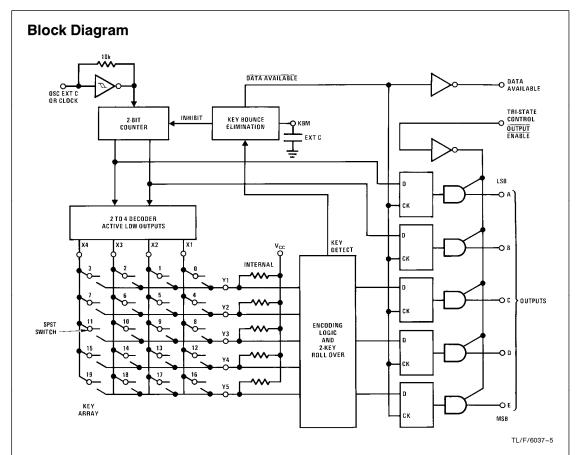

### **Theory of Operation**

The MM74C922/MM74C923 Keyboard Encoders implement all the logic necessary to interface a 16 or 20 SPST key switch matrix to a digital system. The encoder will convert a key switch closer to a 4(MM74C922) or 5(MM74C923) bit nibble. The designer can control both the keyboard scan rate and the key debounce period by altering the oscillator capacitor, C<sub>OSE</sub>, and the key bounce mask capacitor, C<sub>MSK</sub>. Thus, the MM74C922/MM74C923's performance can be optimized for many keyboards.

The keyboard encoders connect to a switch matrix that is 4 rows by 4 columns (MM74C922) or 5 rows by 4 columns (MM74C923). When no keys are depressed, the row inputs are pulled high by internal pull-ups and the column outputs sequentially output a logic "0". These outputs are open drain and are therefore low for 25% of the time and otherwise off. The column scan rate is controlled by the oscillator input, which consists of a Schmitt trigger oscillator, a 2-bit counter, and a 2–4-bit decoder.

When a key is depressed, key 0, for example, nothing will happen when the X1 input is off, since Y1 will remain high. When the X1 column is scanned, X1 goes low and Y1 will go low. This disables the counter and keeps X1 low. Y1 going

low also initiates the key bounce circuit timing and locks out the other Y inputs. The key code to be output is a combination of the frozen counter value and the decoded Y inputs. Once the key bounce circuit times out, the data is latched, and the Data Available (DAV) output goes high.

TL/F/6037-13

If, during the key closure the switch bounces, Y1 input will go high again, restarting the scan and resetting the key bounce circuitry. The key may bounce several times, but as soon as the switch stays low for a debounce period, the closure is assumed valid and the data is latched.

A key may also bounce when it is released. To ensure that the encoder does not recognize this bounce as another key closure, the debounce circuit must time out before another closure is recognized.

The two-key roll-over feature can be illustrated by assuming a key is depressed, and then a second key is depressed. Since all scanning has stopped, and all other Y inputs are disabled, the second key is not recognized until the first key is lifted and the key bounce circuitry has reset.

The output latches feed TRI-STATE, which is enabled when the Output Enable  $(\overline{OE})$  input is taken low.

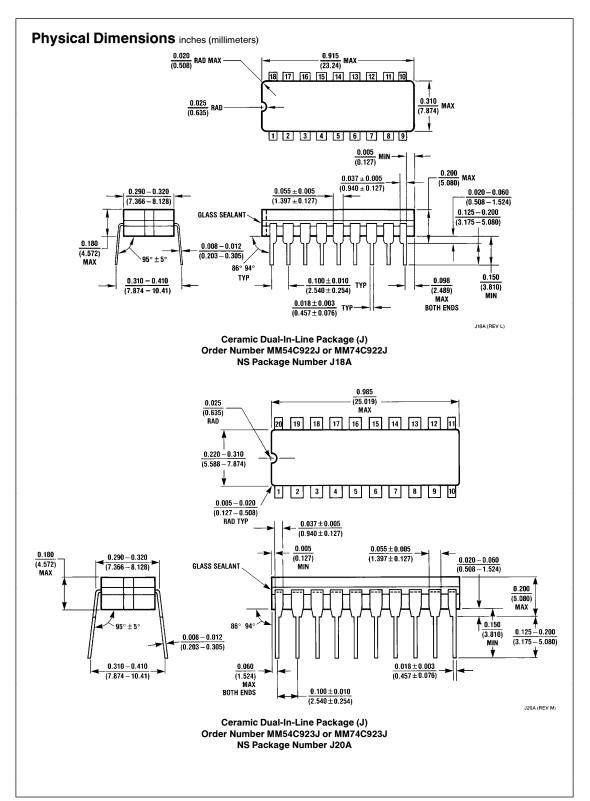

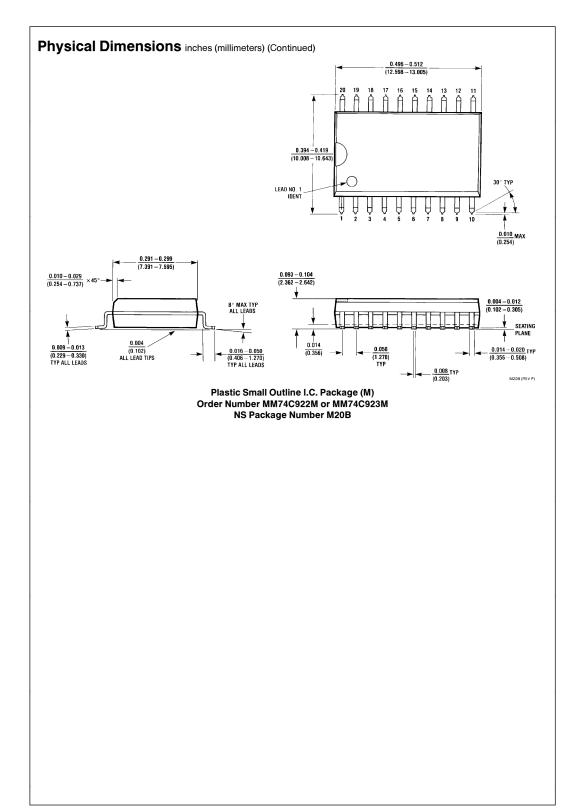

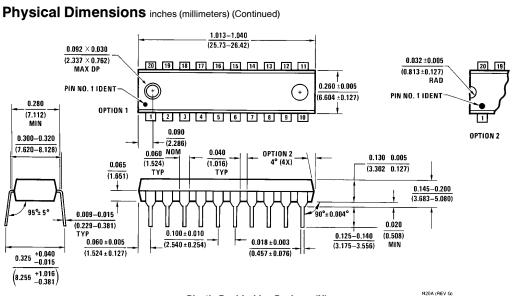

Plastic Dual-In-Line Package (N) Order Number MM54C923N or MM74C923N NS Package Number N20A

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor**

National Semiconducto Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

**National Semiconductor** Europe

Fax: (+49) 0-180-530 85 86 Fax: (+49) U-18U-35U oo oo Email: onjwege etevm2.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tei: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80 **National Semiconductor** Hong Kong Ltd.

13th Floor, Straight Block,

Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon

Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor Japan Ltd.

Tel: 81-043-299-2309

Fax: 81-043-299-2408