SN54178...JOR W PACKAGE

DECEMBER 1972-REVISED DECEMBER 1983

- Typical Maximum Clock Frequency ... 39 MHz

- Three Operating Modes: Synchronous Parallel Łoad Right Shift Hold (Do Nothing)

- Negative-Edge-Triggered Clocking

- D-C Coupling Symplifies System Designs

#### description

These shift registers utilize fully d-c coupled storage elements and feature synchronous parallel inputs and parallel outputs. The SN54179/SN74179 has a direct clear line and complementary output from the D flip-flop, thereby differing from the SN54178/SN74178.

Parallel loading is accomplished by taking the shift input low, applying the four bits of data, and taking the load input high. The data is loaded into the associated flip-flop synchronously and appears at the outputs after a high-to-low transition of the clock. During loading, serial data flow is inhibited.

Shift right is also accomplished on the falling edge of the clock pulse when the shift input is high regardless of the level of the load input. Serial data for this mode is entered at the serial data input.

When both the shift and load inputs are low, clocking of the register can continue; however, data appearing at each output is fed back to the flip-flop input creating a mode in which the data is held unchanged. Thus, the system clock may be left free-running without changing the contents of the register.

| SN74178 J OR N PACKAGE<br>(TOP VIEW) |  |                                 |                                                                    |  |  |  |  |  |  |

|--------------------------------------|--|---------------------------------|--------------------------------------------------------------------|--|--|--|--|--|--|

| B<br>SER<br>QA<br>CLK<br>QB<br>GND   |  | 14<br>13<br>12<br>11<br>10<br>9 | V <sub>CC</sub><br>  C<br>  D<br>  SHIFT<br>  QD<br>  LOAD<br>  QC |  |  |  |  |  |  |

SN54179...JOR W PACKAGE SN74179...JOR N PACKAGE (TOP VIEW)

| CLR<br>B<br>A<br>SER<br>QA<br>CLK |     |    |      |

|-----------------------------------|-----|----|------|

| CLK                               | []6 | 11 | QD   |

| QB                                | []7 | 10 | LOAD |

| GND                               | []8 | 9  | QC   |

|          |          |        |              | FUNCT  | 101      | I TA | BLE |   |      |                 |                 |                 |                  |

|----------|----------|--------|--------------|--------|----------|------|-----|---|------|-----------------|-----------------|-----------------|------------------|

|          | INPUTS   |        |              |        |          |      |     | 0 | UTPU | rs              |                 |                 |                  |

| CI E ADT | CUIT     | 01.00% | CLOCK SERIAL |        | PARALLEL |      |     |   | _    | _               | -               |                 |                  |

| CLEAR.   | SHIFT    | LUAD   | CLUCK        | SERIAL | A        | В    | С   | D | Q.   | QB              | ac              | ٥D              | ₫ <sub>D</sub> † |

| L        | х        | х      | ×            | x      | х        | х    | х   | х | L    | L               | L               | L               | н                |

| н        | <u> </u> | x      | н_           |        | x        | x    | x   | X | QA0  | 0 <sub>B0</sub> | a <sub>co</sub> | QD0             | ο <sub>D0</sub>  |

| н        | L        | L      | ↓ ↓          | x      | x        | х    | х   | х | QAO  | a <sub>B0</sub> | QC0             | Q <sub>D0</sub> | QD0              |

| H I      | L        | н      | ţ            | x      | а        | b    | С   | d | а    | ь               | c               | d               | đ                |

| н        | н        | х      | Ļ            | н      | ×        | х    | х   | х | н    | QAn             | QBn             | QCn             | ācn              |

| н        | н        | х      | ↓ ↓          | L      | X        | х    | х   | х | L    | Q <sub>An</sub> | QBn             | QCn             |                  |

'178, '179<sup>†</sup>

<sup>†</sup>The columns for clear,  $\overline{Q}_{D}$ , and the top line of the table apply for the '179 only.

H = high level (steady state), L = low level (steady state)

X = irrelevant (any input, including transitions)

$\downarrow$  = transition from high to low level

a, b, c, d = the level of steady-state input at inputs A, B, C, or D, respectively.

$\Omega_{AQ}$ ,  $\Omega_{BQ}$ ,  $\Omega_{CQ}$ ,  $\Omega_{DQ}$  = the level of  $\Omega_A$ ,  $\Omega_B$ ,  $\Omega_C$ , or  $\overline{\Omega}_D$ , respectively, before the indicated steady-state input conditions were established.  $\Omega_{An}$ ,  $\Omega_{Bn}$ ,  $\Omega_{Cn}$  = the level of  $\Omega_A$ ,  $\Omega_B$ , or  $\Omega_C$ , respectively, before the most-recent  $\downarrow$  transition of the clock.

----

PRODUCTION DATA This decument contains information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warrenty. Production processing does not necessarily include testing of all parameters.

TTL DEVICES

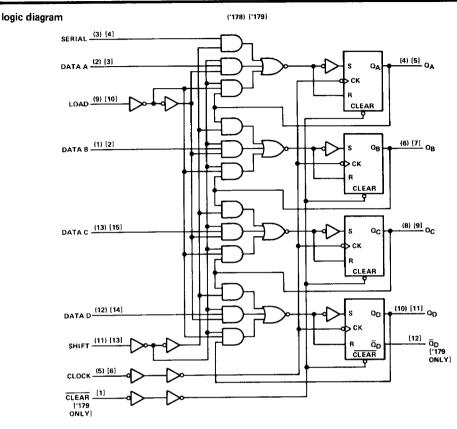

Pin numbers shown on logic notation are for J or N packages.

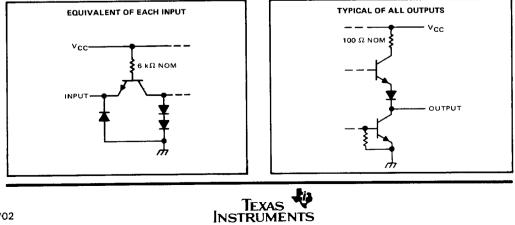

#### schematics of inputs and outputs

POST OFFICE BOX 225012 . DALLAS, TEXAS 75265

| absolute maximum ratings over operating free-air temperature range | (unless otherwise noted) |

|--------------------------------------------------------------------|--------------------------|

|--------------------------------------------------------------------|--------------------------|

| Supply voltage, VCC (see Note 1) |                                        |

|----------------------------------|----------------------------------------|

| Input voltage                    | 5.5 V                                  |

|                                  | -5000000000000000000000000000000000000 |

|                                  | SN74178, SN74179 Circuits              |

| Storage temperature range        | -65°C to 150°C                         |

NOTE 1: Voltage values are with respect to network ground terminal.

#### recommended operating conditions

|                                                  |                                               | SN54178, SN54179 |     |      | SN74178, SN74179 |     |      | UNIT |

|--------------------------------------------------|-----------------------------------------------|------------------|-----|------|------------------|-----|------|------|

|                                                  |                                               | MIN              | NOM | MAX  | MIN              | NOM | MAX  |      |

| Surahu voltage Voo                               |                                               | 4.5              | 5   | 5.5  | 4.75             | 5   | 5.25 | V    |

| Supply voltage, VCC                              |                                               | 1                |     | -800 |                  |     | 800  | μA   |

| High-level output current, IOH                   |                                               | +                |     | 16   |                  |     | 16   | mA   |

| Low-level output current, IOL                    |                                               | +                |     |      | <u> </u>         |     | 25   | MHz  |

| Clock frequency, fclock                          |                                               | 0                |     | 25   | 0                |     | 25   |      |

| Width of clock or clear pulse, tw (see Figure 1) |                                               | 20               |     |      | 20               |     |      | ns   |

|                                                  | Shift (H or L) or load                        | 35               |     |      | 35               |     |      | 4    |

|                                                  | Data                                          | 30               |     |      | 30               |     |      | ns   |

| Setup time, t <sub>su</sub> (see Figure 1)       | Clear-inactive-state<br>(SN54179 and SN74179) | 15               |     |      | 15               |     |      |      |

| Hold time at any input, th                       |                                               | 5                |     |      | 5                |     |      | ns   |

| Operating free-air temperature, TA               |                                               | 55               |     | 125  | 0                |     | 70   | °c   |

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|            |                                        |                                                    | SN54178, SN |              | 178, SN54179 |         | SN74178, SN74179 |      |          |

|------------|----------------------------------------|----------------------------------------------------|-------------|--------------|--------------|---------|------------------|------|----------|

|            | PARAMETER                              | TEST CONDITIONS <sup>†</sup>                       | MIN         | MIN TYP# MAX |              | MIN     | TYP‡             | MAX  | UNI.     |

|            | High-level input voltage               |                                                    | 2           |              |              | 2       |                  |      | [ v      |

| VIH        |                                        |                                                    |             |              | 0.8          |         |                  | 0.8  | V        |

| VIL        | Low-level input voltage                | $V_{CC} = MIN$ , $I_1 = -12 \text{ mA}$            |             |              | -1.5         | <b></b> |                  | -1.5 | l v      |

| VIK        | Input clamp voltage                    | • • • • • • • • • • • • • • • • • • • •            |             |              |              | ┼       |                  |      | <u> </u> |

| ∨он        |                                        | $V_{CC} = MIN, V_{IH} = 2V,$                       | 2.4         | .4 3.4       |              | 2.4     | 3.4              |      | l v      |

|            | High-level output voltage              | V <sub>IL</sub> = 0.8 V, I <sub>OH</sub> = -800 µA |             |              |              |         |                  |      |          |

|            |                                        | $V_{CC} = MIN, V_{1H} = 2V,$                       |             | 0.2          | 0.4          |         | 0.2              | 0.4  | l v      |

| Vol        | Low-level output voltage               | $V_{1L} = 0.8 V$ , $I_{OL} = 16 mA$                |             | 0.2          |              |         |                  |      |          |

| 4          | Input current at maximum input voltage | V <sub>CC</sub> = MAX, V <sub>I</sub> = 5.5 V      |             |              | 1            |         |                  | 1    | mA       |

| <u> </u>   | High-level input current               | Vcc = MAX, Vi = 2.4 V                              |             |              | 40           |         |                  | 40   | μA       |

| <u>'1H</u> |                                        | V <sub>CC</sub> = MAX, V <sub>I</sub> = 0.4 V      | <u> </u>    |              | -1.6         |         |                  | -1.6 | mA       |

| μL         | Low-level input current                |                                                    |             |              |              | -18     |                  | -57  | mA       |

| los        | Short-circuit output current§          | V <sub>CC</sub> = MAX                              | -20         |              | -57          | - 18    |                  |      | -        |

| 1cc        | Supply current                         | V <sub>CC</sub> = MAX, See Note 2                  |             | 46           | 70           |         | 46               | 75   | mA       |

<sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable device

type,

‡All typical values are at  $V_{CC} = 5 V$ ,  $T_A = 25^{\circ}C$ .

<sup>§</sup>Not more than one output should be shorted at a time.

NOTE 2: ICC is measured as follows: a) 4.5 V is applied to serial inputs, load, shift, and clear,

b) Parallel inputs A through D are grounded.

c) 4.5 V is momentarily applied to clock which is then grounded.

| PARAMETER        | FROM<br>(INPUT) | TO<br>(OUTPUT)                                                    | TEST CONDITIONS   | MIN | ТҮР | мах | UNIT |

|------------------|-----------------|-------------------------------------------------------------------|-------------------|-----|-----|-----|------|

| fmax             |                 |                                                                   |                   | 25  | 39  |     | MHz  |

| tPLH .           |                 | ān                                                                |                   |     |     |     | WINZ |

| <b>tPHL</b>      | Clear           | Q <sub>A</sub> , Q <sub>B</sub> , Q <sub>C</sub> , Q <sub>D</sub> | CL=15pF, RL=400Ω, |     | 15  | 23  | ns   |

| tPLH             |                 | <u>~A, ~B, ~C, ~D</u>                                             | See Figure 1      |     | 24  | 36  |      |

| <sup>t</sup> PHL | Clock           | Any output                                                        |                   |     | 17  | 26  |      |

|                  |                 |                                                                   |                   |     | 23  | 35  | ns   |

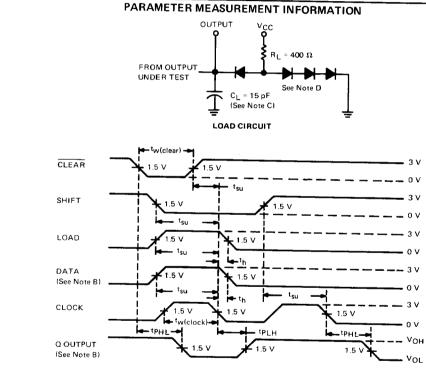

# switching characteristics, V<sub>CC</sub> = 5 V, T<sub>A</sub> = $25^{\circ}$ C

¶f<sub>max</sub> = Maximum clock frequency

tPHL = Propagation delay time, high-to-low-level output

tPLH ≅Propagation delay time, low-to-high-level output

VOLTAGE WAVEFORMS

- NOTES: A. Input pulses are supplied by generators having the following characteristics:  $t_{TLH} \le 10$  ns,  $t_{THL} \le 10$  ns, PRR  $\le 1$  MHz,  $Z_{out} \approx 50 \ \Omega$ .

- B. Data input and Q output are any related pair. Serial and other data inputs are at GND. Serial data input is tested in conjunction with Q<sub>A</sub> output in the shift mode.

- C. CL includes probe and jig capacitance.

- D. All diodes are 1N3064 or equivalent.

FIGURE 1-SWITCHING TIMES

3

This datasheet has been downloaded from:

www.DatasheetCatalog.com

Datasheets for electronic components.

# **Texas Instruments**

http://www.ti.com

This file is the datasheet for the following electronic components:

SN74179 - http://www.ti.com/product/sn74179?HQS=TI-null-null-dscatalog-df-pf-null-wwe