# **ECG**® Semiconductors

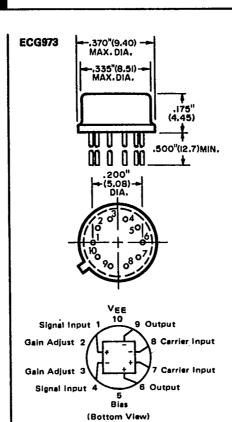

# ECG973, ECG973D

Modulator/Demodulator

## **Features**

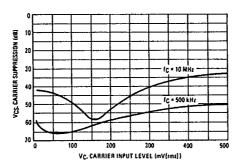

- Excellent carrier suppression 66 dB typ at 0.5 MHz 50 dB typ at 10 MHz

- · Adjustable gain and signal handling

- · Balanced inputs and outputs

- High common mode rejection 86 dB typ

ECG973 is a metal package and ECG973D is a 14 pin DIP. They are silicon monolithic integrated circuits designed for use as a balanced modulator-demodulator where the output voltage is a product of an input voltage and a switching function. Typical applications include suppressed carrier and amplitude modulation, synchronous detection, FM detection, phase detection and chopper applications.

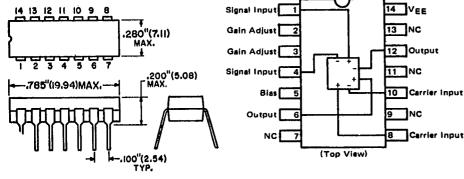

# ECG973D

.CG973, ECG973D

228

i

| Characteristic                                                                                                                                                   | Symbol                                                             | Rating                                      | Unit           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------|----------------|

| Applied Voltage<br>(V6-V7, V3-V1, V9-V7, V9-V8,<br>V7-V4, V7-V1, V8-V4, V6-V8,<br>V2-V5, V3-V5)                                                                  | ΔV                                                                 | 30                                          | Vdc            |

| Differential Input Signal                                                                                                                                        | V <sub>7</sub> , V <sub>8</sub><br>V <sub>4</sub> , V <sub>1</sub> | +5.0<br>+(5+l <sub>5</sub> R <sub>e</sub> ) | Vdc            |

| Maximum Bias Current                                                                                                                                             | 15                                                                 | 10                                          | mA             |

| Power Dissipation (Package<br>Limitation)<br>Dual In-Line Package<br>Derate above T <sub>A</sub> = +25°C<br>Metal Package<br>Derate above T <sub>A</sub> = +25°C | PD                                                                 | 575<br>3.85<br>680<br>4.6                   | mW/°C<br>mW/°C |

| Operating Temperature                                                                                                                                            | T <sub>opg</sub>                                                   | 0 to +70                                    | °C             |

| Storage Temperature Range                                                                                                                                        | T <sub>stg</sub>                                                   | -65 to +150                                 | °C             |

Electrical Characteristics\* ( $V_{CC}$  = +12 Vdc,  $V_{EE}$  =8.0 Vdc,  $I_{B}$  = =1.0 mAdc,  $R_{L}$  =3.9 kQ,  $R_{\theta}$  =1.0 kQ,  $T_{A}$  = +25°C unless otherwise noted.) (All input and output characteristics are single-ended unless otherwise noted.)

| Characteristic                                                                                                                                                                    | Fig. | Note | Symbol     | Min | Тур        | Max | Unit     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------------|-----|------------|-----|----------|

| Carrier Feedthrough  V <sub>C</sub> =60 mV <sub>RMS</sub> sine wave and offset adjusted to zero  f <sub>C</sub> =1.0 kHz f <sub>C</sub> =10 MHz                                   | 5    | 1    | VCFT       |     | 40<br>140  |     | μVRMS    |

| V <sub>C</sub> =300 mVp-p square wave: offset adjusted to zero f <sub>C</sub> =1.0 kHz offset not adjusted f <sub>C</sub> =1.0 kHz                                                |      |      |            |     | 0.04       | 0.4 | mVRMS    |

| Carrier Suppression  f <sub>8</sub> =10 kHz, 300 mV <sub>RMS</sub> f <sub>C</sub> =500 kHz, 60 mV <sub>RMS</sub> sine wave f <sub>C</sub> =10 MHz, 60 mV <sub>RMS</sub> sine wave | 5    | 2    | Vcs        | 40  | 65<br>50   |     | dB<br>k  |

| Transadmittance Bandwidth (Magnitude) (R <sub>L</sub> =50 Q) Carrier Input Port, V <sub>C</sub> =60 mV <sub>RMS</sub> sine wave fs=1.0 kHz, 300 mV <sub>RMS</sub> sine wave       | 8    | 8    | BW3dB      | -   | 300        |     | MHz      |

| Signal Input Port, V <sub>S</sub> =300 mV <sub>RMS</sub> sine wave  V <sub>C</sub>  =0.5 Vdc                                                                                      |      |      |            |     | 80         |     | MHz      |

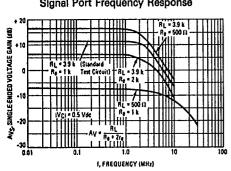

| Signal Gain $V_8 = 100 \text{ mV}_{RMS}$ , f = 1.0 kHz; $ V_C  = 0.5 \text{ Vdc}$                                                                                                 | 10   | 3    | Avs        | 2.5 | 3.5        |     | V/V      |

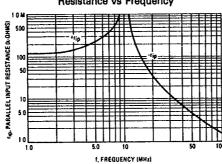

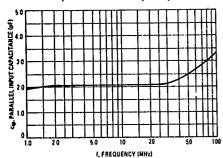

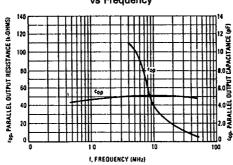

| Single-Ended Input Impedance, Signal<br>Port, f=5.0 MHz<br>Parallel Input Resistance<br>Parallel Input Capacitance                                                                | 6    |      | cip<br>Lib |     | 200<br>2.0 | : : | kΩ<br>pF |

# Electrical Characteristics\* (cont.)

| Characteristic                                                                                          | Fig. | Note | Symbol                             | Min  | Тур        | Max        | Unit             |

|---------------------------------------------------------------------------------------------------------|------|------|------------------------------------|------|------------|------------|------------------|

| Single-Ended Output Impedance,<br>f=10 MHz<br>Parallel Output Resistance<br>Parallel Output Capacitance | 6    |      | r <sub>op</sub><br>c <sub>op</sub> | 1 1  | 40<br>5.0  | ; ;        | kΩ<br>pF         |

| Input Bias Current $I_{bS} = \frac{I_1 + I_4}{2}; I_{bC} = \frac{I_7 + I_8}{2}$                         | 7    |      | l <sub>b</sub> s                   | <br> | 12<br>12   | 88         | μΑ               |

| Input Offset Current<br>IoS=I1 - I4; IoC=I7 - I8                                                        | 7    |      | lioS <br> lioC                     |      | 0.7<br>0.7 | 7.0<br>7.0 | μΑ               |

| Average Temperature Coefficient of Input<br>Offset Current<br>(TA = -55°C to +125°C)                    | 7    |      | TC <sub>lio</sub>                  |      | 2.0        |            | nA/°C            |

| Output Offset Current<br>(16 - 19)                                                                      | 7    |      | llool                              |      | 14         | 80         | μΑ               |

| Average Temperature Coefficient of Output Offset Current (TA = -55°C to +125°C)                         | 7    |      | TC <sub>loo</sub>                  |      | 90         |            | nA/°C            |

| Common-Mode Input Swing, Signal Port, f <sub>8</sub> = 1.0 kHz                                          | 9    |      | CMV                                |      | 5.0        |            | V <sub>p-p</sub> |

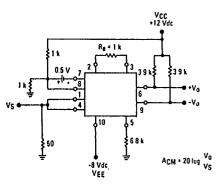

| Common-Mode Gain, Signal Port,<br>f <sub>8</sub> =1.0 kHz,<br>V <sub>C</sub>  =0.5 Vdc                  | 9    |      | ACM                                |      | -85        |            | dB               |

| Common-Mode Quiescent Output Voltage<br>(Pin 6 or Pin 9)                                                | 10   |      | V <sub>o</sub>                     |      | 8.0        |            | Vdc              |

| Differential Output Voltage Swing<br>Capability                                                         | 10   |      | V <sub>out</sub>                   | -    | 8.0        |            | V <sub>p-p</sub> |

| Power Supply Current<br>I6+I9<br>I1Q                                                                    | 7    | 6    | lcc<br>lEE                         |      | 2.0<br>3.0 | 4.0<br>5.0 | mAdc             |

| DC Power Dissipation                                                                                    | 7    | 5    | PD                                 | -    | 33         |            | mW               |

<sup>\*</sup> Pin number references pertain to this device when packaged in a metal can. To ascertain the corresponding pin numbers for plastic packaged devices refer to the first page of this specification.

# Notes

# 1. Carrier Feedthrough

Carrier feedthrough is defined as the output voltage at carrier frequency with only the carrier applied (signal voltage = 0).

Carrier null is achieved by balancing the currents in the differential amplifier by means of a bias trim potentiometer (R1 of Figure 5).

# Carrier Suppression

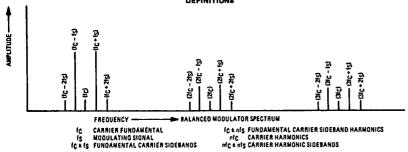

Carrier suppression is defined as the ratio of each sideband output to carrier output for the carrier and signal voltage levels specified.

ECG973, ECG973D

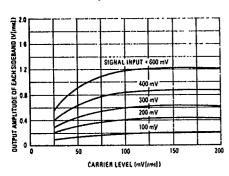

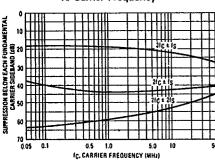

Carrier suppression is very dependent on carrier input level, as shown in Figure 22. A low value of the carrier does not fully switch the upper switching devices, and results in lower signal gain, hence lower carrier suppression. A higher than optimum carrier level results in unnecessary device and circuit carrier feedthrough, which again degenerates the suppression figure. The ECG973 has been characterized with a 60 mV(RMS) sinewave carrier input signal. This level provides optimum carrier suppression at carrier frequencies in the vicinity of 500 kHz, and is generally recommended for balanced modulator applications.

Carrier feedthrough is independent of signal level, Vg. Thus carrier suppression can be maximized by operating with large signal levels. However, a linear operating mode must be maintained in the signal-input transistor pair-or harmonics of the modulating signal will be generated and appear in the device output as spurious sidebands of the suppressed carrier. This requirement places an upper limit on input-signal amplitude (see Note 3 and Figure 20). Note also that an optimum carrier level is recommended in Figure 22 for good carrier suppression and minimum spurious sideband generation.

At higher frequencies circuit layout is very important in order to minimize carrier feedthrough. Shielding may be necessary in order to prevent capacitive coupling between the carrier input leads and the output leads.

Signal Gain and Maximum Input Level Signal gain (single-ended) at low frequencles is defined as the voltage gain,

$$A_{VS} = \frac{V_0}{V_S} = \frac{R_L}{R_\theta + 2r_\theta} \text{ where } r_\theta = \frac{26 \text{ mV}}{I_5 \text{ (mA)}}$$

A constant do potential is applied to the carrier input terminals to fully switch two of the upper transistors "on" and two transistors "off" ( $V_c = 0.5 \text{ Vdc}$ ). This in effect forms a cascode differential amplifier,

Linear operation requires that the signal input be below a critical value determined by Rr and the bias current in

Note that in the test circuit of Figure 10, Vs corresponds to a maximum value of 1 volt peak.

# Common-Mode Swing

The common-mode swing is the voltage which may be applied to both bases of the signal differential amplifier, without saturating the current sources or without saturating the differential amplifier itself by swinging it into the upper switching devices. This swing is variable depending on the particular circuit and biasing conditions chosen (see Note 6).

# **Power Dissipation**

Power dissipation, PD, within the integrated circuit package should be calculated as the summation of the

voltage-current products at each port, i.e., assuming  $V_9 = V_6$ ,  $I_5 = I_6 = I_9$  and ignoring base current,  $P_D = 2 I_5 (V_6 - I_6)$ V<sub>10</sub>) + I<sub>5</sub> (V<sub>6</sub> - V<sub>10</sub>) where subscripts refer to pin numbers.

# **Design Equations**

The following is a partial list of design equations needed to operate the circuit with other supply voltages and input conditions. See Note 3 for Re equation.

## A. Operating Current

1,7E

The internal bias currents are set by the conditions at pin 5. Assume:

IB << IC for all transistors

then:

$$R_{5} = \frac{V^{-} - \Phi}{I_{5}} - 500 \Omega$$

where:

R5 is the resistor between pin 5 and ground  $\Phi = 0.75 \text{ V at T}_{A} = +25^{\circ}\text{C}$

The ECG973 has been characterized for the condition I5=1.0 mA and is the generally recommended value.

B. Common-Mode Quiescent Output Voltage

#### Blasing

The ECG973 requires three dc bias voltage levels which must be set externally. Guidelines for setting up these three levels include maintaining at least 2 volts collector-base bias on all transistors while not exceeding the voltages given in the absolute maximum rating table:

30 Vdc

$$\geq$$

[(V<sub>6</sub>,V<sub>9</sub>) - (V<sub>7</sub>,V<sub>8</sub>)]  $\geq$  2 Vdc

30 Vdc

$$\geq$$

[(V7,V8) - (V1,V4)]  $\geq$  2.7 Vdc

30 Vdc

$$\geq [(V_1, V_4) - (V_5)] \geq 2.7$$

Vdc

The foregoing conditions are based on the following approximations:

$$V_6 = V_9$$

,  $V_7 = V_8$ ,  $V_1 = V_4$

Bias currents flowing into pins 1, 4, 7, and 8 are transistor base currents and can normally be neglected if external bias dividers are designed to carry 1.0 mA or more.

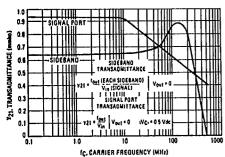

# Transadmittance Bandwidth

Carrier transadmittance bandwidth is the 3-dB bandwidth of the device forward transadmittance as defined by:

Signal transadmittance bandwidth is the 3-dB bandwidth of the device forward transadmittance as defined by:

$$\gamma 21S = \frac{I_0 \text{ (signat)}}{V_8 \text{ (signat)}} | V_0 = 0.5 \text{ Vdc, } V_0 = 0$$

\*Pin number references pertain to this device when packaged in a metal can. To ascertain the corresponding pin numbers for plastic packaged devices refer to the first page of this specification sheet.

# Coupling and Bypass Capacitors C1 and

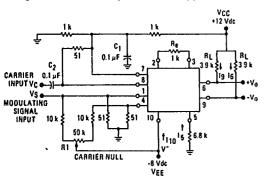

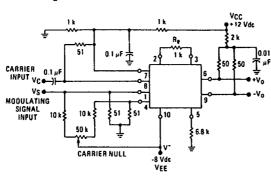

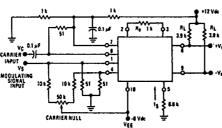

Capacitors C<sub>1</sub> and C<sub>2</sub> (Figure 5) should be selected for a reactance of less than 5.0 ohms at the carrier frequency.

# **Performance Characteristics**

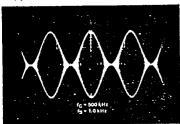

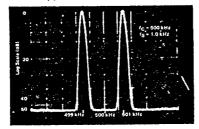

Figure 1 -Suppressed Carrier Output Waveform

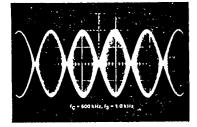

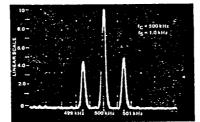

Figure 3 -Amplitude Modulation Output Waveform

# 10. Output Signal, Vo

The output signal is taken from pin 6 and 9, either balanced or single-ended. Figure 12 shows the output levels of each of the two output sidebands resulting from variations in both the carrier and modulating signal inputs with a single-ended output connection.

# 11. Signal Port Stability

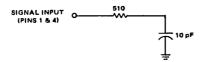

Under certain values of driving source impedance, oscillation may occur. In this event, an RC suppression network should be connected directly to each input using short leads. This will reduce the Q of the source-tuned circuits that cause the oscillation.

An alternate method for low-frequency applications is to insert a 1 k-ohm resistor in series with the inputs, pins 1 and 4. In this case input current drift may cause serious degradation of carrier suppression.

Figure 2 -Suppressed Carrier Spectrum

Figure 4 ---Amplitude Modulation Spectrum

Pin number references pertain to this device when packed in a metal can. To ascertain the corresponding pin numbers for plastic packaged devices refer to the first page of this specification.

ECG973, ECG973D

# **Test Circuits**

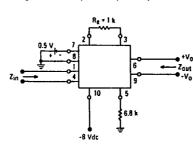

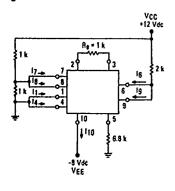

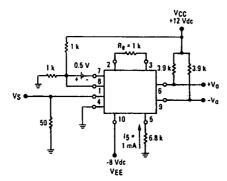

Figure 5 - Carrier Rejection and Suppression

Figure 6 - Input-Output Impedance

Figure 7 — Bias and Offset Currents

Figure 8 - Transconductance Bandwidth

Figure 9 -- Common-Mode Gain

Figure 10 - Signal Gain and Output Swing

Pin number references pertain to this device when packaged in a metal can. To ascertain the corresponding pin numbers for plastic packaged devices refer to the first page of this specification.

# **Typical Characteristics**

Typical characteristics were obtained with circuit shown in Figure 5,  $f_C$  = 500 kHz (sine wave),  $V_C$  = 60 mV(RMS),  $f_S$  = 1 kHz,  $V_S$  = 300 mV(RMS),  $T_A$  = +25°C unless otherwise noted.

Figure 11 — Sideband Output vs Carrier Levels

Figure 12 —

Signal Port Parallel Equivalent Input

Resistance vs Frequency

17E

Figure 13 — Signal Port Parallel Equivalent Input Capacitance vs Frequency

Figure 14 — Single-Ended Output Impedance vs Frequency

Figure 15 — Sideband and Signal Port Transadmittances vs Frequency

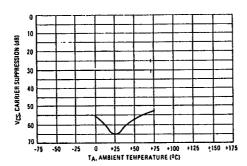

Figure 16 — Carrier Suppression vs Temperature

# Typical Characteristics (cont.)

Figure 17 — Signal Port Frequency Response

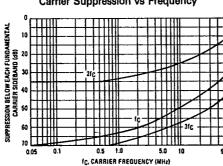

Figure 18 — Carrier Suppression vs Frequency

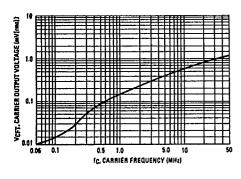

Figure 19 — Carrier Feedthrough vs Frequency

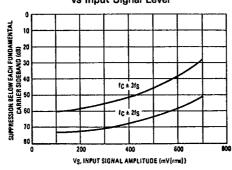

Figure 20 — Sideband Harmonic Suppression vs Input Signal Level

Figure 21 —

Suppression of Carrier Harmonic Sidebands

vs Carrier Frequency

Figure 22 — Carrier Suppression vs Carrier Input Level

# **Typical Operation Information**

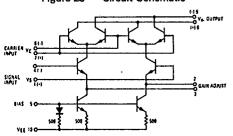

Figure 23 - Circuit Schematic

Figure 24 — Modulator Circuit

Figure 25 - AC and DC Voltage Gain and Output Frequencies

| Carrier<br>Input<br>Signal (V <sub>C</sub> ) | Approximate<br>Voltage Gain                       | Output<br>Signal<br>Frequency(s) |

|----------------------------------------------|---------------------------------------------------|----------------------------------|

| Low-level dc                                 | 2(RE+2re) KT                                      | fM                               |

| High-level do                                | R <sub>L</sub><br>R <sub>E</sub> +2r <sub>e</sub> | fM                               |

| Carrier<br>Input<br>Signal (V <sub>C</sub> )                          | Approximate<br>Voltage Gain                                   | Output<br>Signal<br>Frequency(s |  |  |

|-----------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------|--|--|

| Low-level ac                                                          | $\frac{R_{L}V_{C}(rms)}{2\sqrt{2}\frac{KT}{q}(R_{E}+2r_{e})}$ | fc±fM                           |  |  |

| High-level ac 0.637 R <sub>L</sub><br>R <sub>E</sub> +2r <sub>e</sub> |                                                               | fc±fM,<br>3fc±fM,<br>5fc±fM     |  |  |

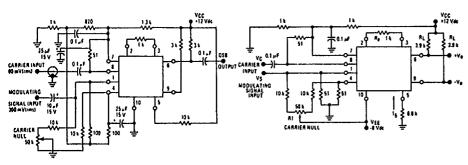

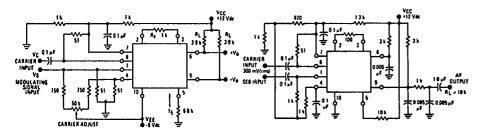

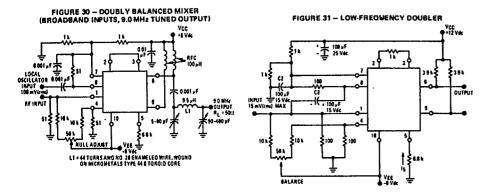

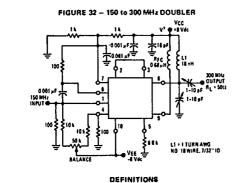

# TYPICAL APPLICATIONS

FIGURE 26 - BALANCED MODULATOR (+12 Vdc SINGLE SUPPLY)

FIGURE 27 - BALANCED MODULATOR-DEMODULATOR

FIGURE 28 - AM MODULATOR CIRCUIT

FIGURE 29 - PRODUCT DETECTOR (+12 Vdc SINGLE SUPPLY)

Pin number references pertain to this device when packaged in a metal can. To ascertain the corresponding pin numbers for plastic packaged devices refer to the first page of this specification.

ECG973, ECG973D

236

State Charle

Pin number references pertain to this device when packaged in a metal can. To ascertain the corresponding pin numbers for plastic packaged devices refer to the first page of this specification.