# **ECG**<sup>®</sup> Semiconductors

**ECG1255**

**PLL Frequency Synthesizer**

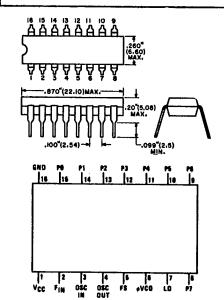

T-45-19-13

#### **Features**

- Single power supply

- Low power CMOS technology

- Binary input channel select code

- 5 kHz or 10 kHz output from oscillator divide

- On-chip oscillator

- Pull-down resistors on programmable divider inputs

- Low voltage operation—5 V

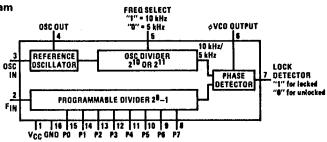

The ECG1255 device contains phase locked loop circuits useful for frequency synthesizer applications in CB transceivers. The device operates off a single power supply and contains an oscillator, a 2¹º or 2¹¹ divider chain, a binary input programmable divider, and phase detector circuitry. The device may be used in double I.F. or single I.F. systems. A 10.24 MHz or 5.12 MHz quartz crystal is used to determine the reference frequency. The inputs to the programmable divider are standard binary signals. Selection of a channel is accomplished by mechanical switches or by external electronic programming of the programmable divider.

The ØVCO output provides a high level voltage (sources current) when the VCO frequency is lower than the lock frequency, and ØVCO provides a low level voltage (sinks current) when the VCO frequency is higher than the lock frequency. The ØVCO output goes to a high impedance condition under lock conditions, and the lock detector output LD goes to a high state under lock conditions.

#### Pin Description

| P0-P8        | Programmable divider inputs                                             |

|--------------|-------------------------------------------------------------------------|

| FIN          | Frequency input from VCO (mixed down)                                   |

| OSC IN       | Oscillator amplifier input terminal                                     |

| OSC OUT      | Oscillator amplifier output terminal                                    |

| LD           | Lock detector                                                           |

| øvco         | Output of phase detector for control of the VCO                         |

| FS           | Frequency division select to kHz or 5 kHz — "1" is 10 kHz, "0" is 5 kHz |

| 5.12 MHz OUT | OSC Frequency divided by 2                                              |

output

### **Absolute Maximum Ratings**

| Characteristic        | Symbol           | Rating      | Unit |

|-----------------------|------------------|-------------|------|

| Supply Voltage        | V <sub>cc</sub>  | 7           | ٧    |

| Operating Temperature | Topg             | -30 to +75  | °C   |

| Storage Temperature   | T <sub>stg</sub> | -40 to +125 | °C   |

597

ECG1255

# **Truth Table**

Truth table for binary inputs to programmable divider.

FOUT = FIN/N

1 = High voltage level, VOH 0 = Low voltage level, VOL

X = Don't care

| N           | P8 | P7 | P6 | P5 | P4 | Р3 | P2 | P1 | PO |

|-------------|----|----|----|----|----|----|----|----|----|

| 1           | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | Х  |

| N<br>1<br>2 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  |

| 511         |    |    |    |    |    |    |    |    |    |

T-45-19-13

| Block | Diagram |

|-------|---------|

|       |         |

#### Electrical Characteristics (T<sub>A</sub> = 25°C)

| Characteristic                                                    | Symbol | Test Condition                                                                                                  | Min                      | Тур | Max        | Unit                     |

|-------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------|--------------------------|-----|------------|--------------------------|

| Supply Voltage                                                    | Vcc    |                                                                                                                 | 4.5                      | 5.0 | 5.5        | V                        |

| Supply Current                                                    | lcc    | Freq @ Osc In = 10<br>MHz, @ F <sub>IN</sub> = 2.5<br>MHz, All Other I/O<br>Pins Open,<br>V <sub>CC</sub> = 5 V |                          | 3   | 10         | mA                       |

| Logical "1" Input Voltage<br>P0-P8, FS, FIN                       | VIN(1) |                                                                                                                 | V <sub>CC</sub> -<br>0.4 |     |            | ٧                        |

| Logical "0" Input Voltage<br>P0-P8, FS, F <sub>IN</sub>           | VIN(0) |                                                                                                                 |                          |     | 0.4        | <b>V</b>                 |

| Logical "1" Output Voltage<br>5.12 MHz Out, LD<br>ØVCO<br>Osc Out |        | IO = 0.5 mA<br>IO = 0.4 mA<br>IO = 0.25 mA                                                                      | V <sub>cc</sub> -<br>0.5 |     |            | ٧                        |

| Logical "0" Output Voltage<br>ØVCO, 5.12 MHz Out,LD<br>Osc Out    |        | I <sub>O</sub> = 0.5 mA<br>I <sub>O</sub> = 0.25 mA                                                             |                          |     | 0.5        | >                        |

| Logical "1" Input Current<br>FS (Pull-Up)<br>P0-P8 (Pull-Down)    |        | V <sub>CC</sub> = 5 V                                                                                           | Б                        | 20  | 1.0<br>50  | μ <b>Α</b><br>μ <b>Α</b> |

| Logical "0" Input Current<br>P0-P8 (Pull-Down)<br>FS (Pull-Up)    |        | V <sub>cc</sub> = 5 V                                                                                           | 10                       | -35 | 1.0<br>100 | μ <b>Α</b><br>μ <b>Α</b> |

| Toggle Frequency @ FIN                                            |        |                                                                                                                 | 3                        |     |            | MHz                      |

| Oscillator Frequency @<br>Osc in                                  |        |                                                                                                                 | 10.24                    |     |            | MHz                      |

| Three State Leakage @ ØVCO                                        |        |                                                                                                                 |                          |     | 1.0        | μΑ                       |

ECG1255

598

T-45-19-13

# Typical Applications

# Introduction to Frequency Synthesis

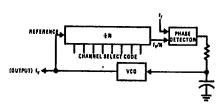

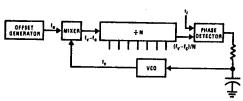

The components of a frequency synthesizer are shown in Figure 1. The voltage controlled oscillator produces the desired output frequencies spaced  $f_V$  Hz apart acording to the relation:

$$f_V = f_r N$$

The reference frequency, fr, must be equal to or less than the (channel) spacing between the frequencies being synthesized.

Figure 1. Basic Frequency Synthesizer

Although simple in concept, the circuit of Figure 1 has certain difficulties. In CB, we are synthesizing the following frequencies:

| Ch 1  | 26.965 |  |  |

|-------|--------|--|--|

| Ch 2  | 26.975 |  |  |

| •     | •      |  |  |

| •     | •      |  |  |

| Ch 23 | 27.225 |  |  |

Although the channel spacing is 10 kHz, a reference frequency of 5 kHz would be necessary due to the odd 5 kHz in the assigned channel. This in itself poses no problem; however, present technology limits the counting speed of programmable dividers to something less than 5 MHz, ruling out the approach shown in Figure 1.

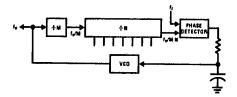

Two solutions to this problem are shown in Figure 2.

Frequency prescaling shown in Figure 2 (a) reduces the VCO frequency by M (a fixed number) to a frequency that can be divided by the programmable counter. The reference frequency  $f_r$  must also be reduced by M. In the case of CB, if M = 10,  $f_V$  = 26.965 MHz, the input to the programmable divider will be 2.6965 MHz, and the 5 kHz reference frequency will be reduced to 500 Hz. This poses problems in speed of response of the phase locked loop.

Figure 2 (a). Frequency Prescaling

Figure 2 (b). Frequency Offset

The second technique mixes the output frequency of the VCO with a stable fixed frequency to obtain a related reference frequency.

$$f_V = Nf_r + f_O$$

This technique has the advantage of allowing a 10 kHz reference frequency in the loop instead of 5 kHz.

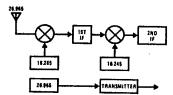

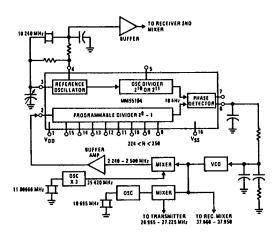

Further complexity arises when one considers that the synthesizer must also generate a local oscillator signal as well as a transmitter input signal for the radio (Figure 3). A system which provides these frequencies, as well as the proper offset to allow the programmable divider to operate within its limits is shown in the typical applications diagrams (Figure 4). The only departure from the ideal situation shown in Figure 3 is that the first IF frequency of 10.7 MHz must be changed to 10.695 MHz (a change of 5 kHz).

Figure 3. Signals Needed to Transmit and Receiver Ch 1

599

ECG1255

T-45-19-13

Figure 4. 3-Crystal Application

ECG1255

600