#### BU508A; BU508D

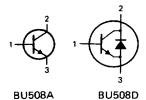

High-voltage, high-speed switching npn transistor in SOT93A envelope intended for use in horizontal deflection circuits of colour television receivers. The BU508D has an integrated efficiency diode.

#### QUICK REFERENCE DATA

| Collector-emitter voltage                                |                    |      |        |    |

|----------------------------------------------------------|--------------------|------|--------|----|

| peak value; VBE = 0                                      | VCESM              | max. | 1500 \ | ٧  |

| Collector-emitter voltage (open base)                    | VCEO               | max. | 700 '  | ٧  |

| Collector current (DC)                                   | 1 <sub>C</sub>     | max. | 8 /    | Α  |

| Collector current peak value                             | ICM                | max. | 15 /   | Α  |

| Total power dissipation<br>up to T <sub>mb</sub> = 25 °C | P <sub>tot</sub>   | max. | 125 \  | w  |

| Collector-saturation voltage                             |                    |      |        |    |

| I <sub>C</sub> = 4.5 A; I <sub>B</sub> = 2 A             | V <sub>CEsat</sub> | max. | 1 '    | V  |

| Saturation collector current                             | <sup>I</sup> Csat  | typ. | 4.5    | Α  |

| Diode forward voltage (BU508D)                           |                    |      |        |    |

| I <sub>F</sub> = 4.5 A                                   | ٧ <sub>F</sub>     | typ. | 1.6    | ٧  |

| Fall time                                                |                    |      |        |    |

| I <sub>CM</sub> = 4.5 A; I <sub>B(on)</sub> = 1.4 A      | tf                 | typ. | 0.7    | μs |

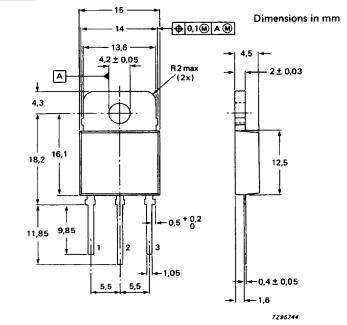

## MECHANICAL DATA

Fig. 1 SOT93A.

1 = base

2 = collector

3 = emitter

Collector connected to mounting base.

7110826 0077463 365

BU508A; BU508D

| R | ۸ | TI | N | c |

|---|---|----|---|---|

Limiting values in accordance with the Absolute Maximum System (IEC 134)

| - The Absolute Maximum                                                                         | 1 3 ystem (IEC )     | 34)          |              |     |

|------------------------------------------------------------------------------------------------|----------------------|--------------|--------------|-----|

| Collector-emitter voltage                                                                      |                      |              |              |     |

| peak value; V <sub>BE</sub> = 0                                                                | VCESM                | max.         | 1500         | V   |

| Collector-emitter voltage (open base)                                                          | VCEO                 | max.         | 700          | ٧   |

| Collector current (DC)                                                                         | 1 <sub>C</sub>       | max.         | 8            | Α   |

| Collector current peak value                                                                   | <sup>1</sup> CM      | max.         | 15           | Α   |

| Base current (DC)                                                                              | I <sub>B</sub>       | max.         | 4            | Α   |

| Base current (peak value)                                                                      | IBM                  | max.         | 6            | Α   |

| Reverse base current (DC or average over any 20 ms period)                                     | −¹B(AV)              | max.         | 100          | mΑ  |

| Reverse base current* (peak value)                                                             | — <sup>I</sup> ВМ    | max.         | 5            | Α   |

| Total power dissipation<br>up to T <sub>mb</sub> = 25 °C                                       | P <sub>tot</sub>     | max.         | 125          |     |

| Storage temperature range                                                                      | T <sub>stg</sub>     | _            | -65 to + 150 | οс  |

| Junction temperature                                                                           | T <sub>i</sub>       | max.         | 150          | οС  |

|                                                                                                | ,                    |              |              |     |

| THERMAL RESISTANCE                                                                             |                      |              |              |     |

| From junction to mounting base                                                                 | R <sub>th j-mb</sub> | #            | 1            | K/W |

| CHARACTERISTICS                                                                                |                      |              |              |     |

| T <sub>j</sub> = 25 °C unless otherwise specified                                              |                      |              |              |     |

| Collector cut-off current**                                                                    |                      |              |              |     |

| V <sub>BE</sub> = 0; V <sub>CE</sub> = V <sub>CESMmax</sub>                                    | CES                  | max.         | 1            | mΑ  |

| $V_{BE} = 0$ ; $V_{CE} = V_{CESMmax}$ ; $T_j = 125  {}^{\circ}C$                               | CES                  | max.         | 2            | mΑ  |

| Emitter cut-off current                                                                        |                      |              |              |     |

| V <sub>EB</sub> = 6 V; I <sub>C</sub> = 0                                                      | <sup> </sup> EBO     | max.         | 10           | mΑ  |

| Collector-emitter sustaining voltage<br>I <sub>B</sub> = 0; I <sub>C</sub> = 100 mA; L = 25 mH | V                    |              | 700          |     |

| Saturation voltages                                                                            | V <sub>CEOsust</sub> | min.         | 700          | V   |

| I <sub>C</sub> = 4.5 A; I <sub>B</sub> = 2 A                                                   | V <sub>CEsat</sub>   | max.         | 1            | V   |

| •                                                                                              | VBEsat               | max.         | 1.3          | -   |

|                                                                                                | BESat                | max.         | 1.5          | ٧   |

| DC current gain                                                                                |                      |              |              |     |

| $I_C = 100 \text{ mA}; V_{CE} = 5 \text{ V}$                                                   | hFE                  | min.         | 6            |     |

|                                                                                                | pEE<br>pEE           | typ.<br>max. | 13<br>30     |     |

| Transition frequency at f ≈ 5 MHz                                                              |                      | 111471,      | 30           |     |

| $I_C = 0.1 \text{ A}; V_{CE} = 5 \text{ V}$                                                    | f <sub>T</sub>       | typ.         | 7            | MHz |

| Collector capacitance at f = 1 MHz                                                             | ,                    |              |              |     |

| $I_E = I_e = 0; V_{CB} = 10 \text{ V}$                                                         | C <sub>c</sub>       | typ.         | 125          | ρF  |

|                                                                                                |                      |              |              |     |

<sup>\*</sup> Turn-off current.

# 7110826 0077464 2T1 **-**

December 1991

<sup>\*\*</sup> Measured with half-sinewave voltage (curve tracer).

250 200 1C (mA) 100 VCE (V)

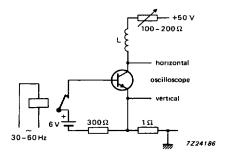

Fig. 2 Test circuit for VCEOsust-

Fig. 3 Oscilloscope display for VCEOsust-

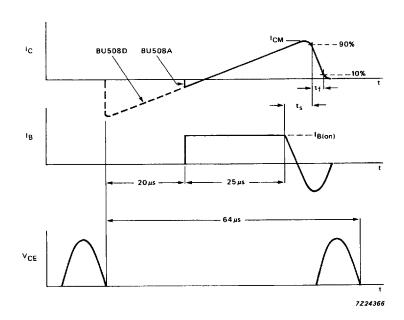

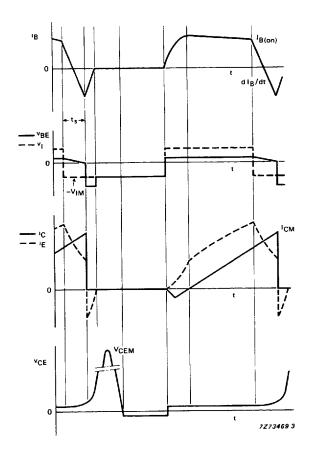

Fig. 4 Switching times waveforms;  $I_{CM}$  = 4.5 A;  $I_{B(on)}$  = 1.4 A;  $I_{B}$  = 6  $\mu$ H;  $-V_{BB}$  = 4 V;  $-dI_{B}/dt$  = 0.6 A/ $\mu$ s; typical value of  $I_{S}$  = 6.5  $\mu$ s; typical value of  $I_{F}$  = 0.7  $\mu$ s.

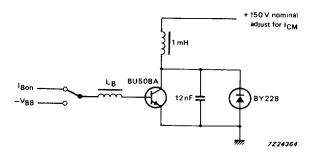

Fig. 5 Switching times test circuit (BU508A).

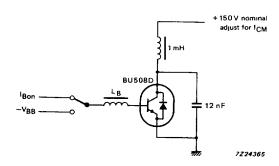

Fig. 6 Switching times test circuit (BU508D).

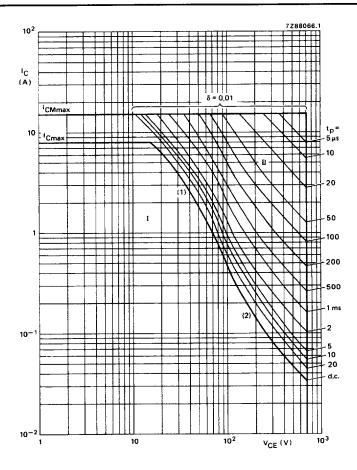

- (1) Ptot max line.

- (2) Second-breakdown limits (independent of temperature).

- I Region of permissible DC operation.

- II Permissible extension for repetitive pulse operation.

Fig. 7 Safe operating area;  $T_{mb}$  < 25 °C.

BU508A; BU508D

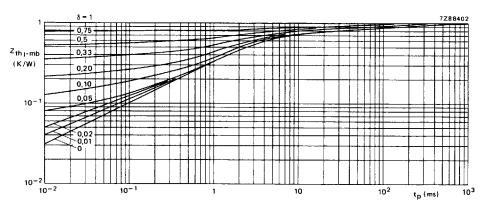

Fig. 8 Pulse power rating chart.

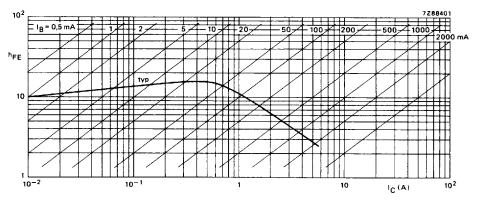

Fig. 9 Typical values DC current gain at  $V_{CE} = 5 \text{ V}$ ;  $T_{mb} = 25 \text{ °C}$ .

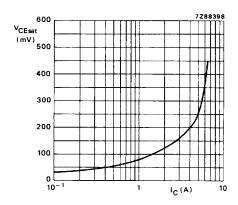

Fig. 10 Typical values  $I_C/I_B = 2$ ;  $T_j = 25$  °C.

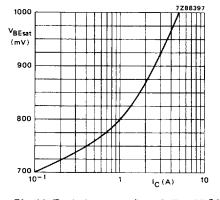

Fig. 11 Typical values  $I_C/I_B = 2$ ;  $T_i = 25$  °C.

■ 7110826 0077468 947 ■■

December 1991

BU508A; BU508D

#### APPLICATION INFORMATION - HORIZONTAL DEFLECTION CIRCUIT WITH BU508A/D

In designing horizontal deflection circuits, allowance has to be made for component and operating spreads in order not to exceed any Absolute Maximum Rating. Extensive analysis has shown that, for the peak collector current and the collector emitter voltage of the output transistor, the total allowance need not be higher than 15% and, the following recommended base-drive and heatsink conditions are based on this figure.

To simplify the presentation the design curves given refer to nominal conditions. Where the collector current will be modulated by the E-W correction circuit the average value of the peak collector current applies, if the modulation is less than 10%.

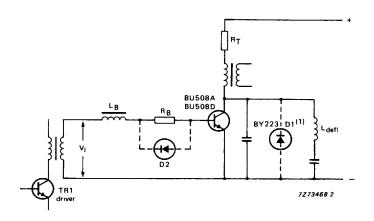

The BU508D is a BU508A with an integrated efficiency diode without a parasitic base-emitter resistor. Therefore a circuit optimized for a BU508A can use a BU508D without alterations. N.B. if a BU508D is used total device dissipation is increased due to the integrated diode losses.

To obtain a short fall time and minimum turn-off dissipation, with a high-voltage transistor, the storage time must be sufficiently long and, during turn-off, the negative base-emitter voltage must be sufficiently high. Both requirements can easily be realized by including a small coil in series with the base of the output transistor. To reduce base current variations a series base resistor is added to most designs. This has the disadvantage of reducing the energy in the base inductance during turn-off which, in turn, reduces the negative base-emitter voltage. This with large resistor values may lead to an insufficient negative voltage for correct device turn-off. This can be improved by providing a shunt diode or capacitor in parallel with the base resistor. Instead of giving various detailed base circuits based on these considerations, it is a more direct approach to specify the recommended —dlg/dt (see Fig. 15).

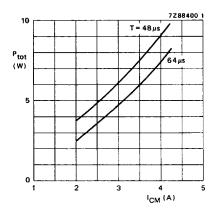

The maximum transistor dissipation depends largely on the tolerance in the drive conditions. The dissipation given in Fig. 16 allows for base current and  $-dl_B/dt$  tolerances of  $\pm$  15%. The curve applies to a limit-case transistor at a mounting base temperature of 85 °C. The thermal resistance for the heatsink can be calculated from:

$$R_{th\ mb-a} = \frac{85 - T_{amb\ max}}{P_{tot\ max}}$$

In which Tamb max is the maximum ambient temperature of the transistor.

In order to assure a value of thermal resistance at which thermal stability is achieved, the minimum value for  $T_{amb}$  in the above equation is 45  $^{\rm oC}$ .

BU508A; BU508D

#### **APPLICATION INFORMATION (continued)**

(1) Not required for this circuit when BU508D is used.

Fig. 12 Simplified horizontal deflection circuit.

Fig. 13 Fundamental waveforms (BU508A).

BU508A; BU508D

#### **APPLICATION INFORMATION (continued)**

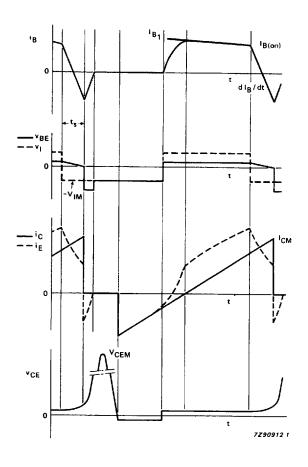

Fig. 14 Fundamental waveforms (BU508D).

#### BU508A; BU508D

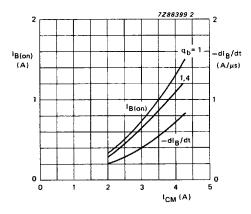

Fig. 15 Nominal end value of the base current and its rate of fall during turn-off as a function of nominal peak collector current.

A 15% spread allowance is included on these nominal values.  $Q_B$  is defined as  $I_{B1}/I_{B(on)}$  (see Fig. 14).

The reverse drive voltage during the storage and fall time ( $-V_{\mbox{IM}}$ ) must be  $> 2~\mbox{V}$ .

Fig. 16 Total dissipation of a limit-case transistor under maximum operating conditions for 625 and 819 lines ( $T_{mb}$  = 85  $^{\circ}$ C).