# **HCF4034B**

# 8 STAGE STATIC BIDIRECTIONAL PARALLEL/SERIAL INPUT OUTPUT BUS REGISTER

- BIDIRECTIONAL PARALLEL DATA INPUT

- PARALLEL OR SERIAL INPUTS/PARALLEL OUTPUTS

- ASYNCHRONOUS OR SYNCHRONOUS PARALLEL DATA LOADING.

- PARALLEL DATA-INPUTS ENABLED ON "A" DATA LINES (3-STATE OUTPUT)

- DATA RECIRCULATION FOR REGISTER EXPANSION

- MULTIPACKAGE REGISTER EXPANSION

- FULLY STATIC OPERATIONAL : DC to 5MHz (Typ.) at V<sub>DD</sub> = 10V

- QUIESCENT CURRENT SPECIF. UP TO 20V

- INPUT LEAKAGE CURRENT I<sub>I</sub> = 100nA (MAX) AT V<sub>DD</sub> = 18V T<sub>A</sub> = 25°C

- 100% TESTED FOR QUIESCENT CURRENT

- MEETS ALL REQUIREMENTS OF JEDEC JESD13B "STANDARD SPECIFICATIONS FOR DESCRIPTION OF B SERIES CMOS DEVICES"

HCF4034B is a monolithic integrated circuit fabricated in Metal Oxide Semiconductor technology available in SOP packages.

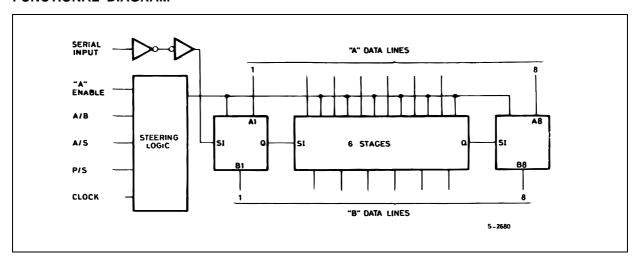

HCF4034B is a static eight-stage parallel-or serial-input parallel-output register. It can be used to: 1) bidirectionally transfer parallel information between two buses; 2) convert serial data to parallel form and direct the parallel data to either

#### **ORDER CODES**

| PACKAGE | TUBE       | T & R         |

|---------|------------|---------------|

| SOP     | HCF4034BM1 | HCF4034M013TR |

of the two buses; 3) store (recirculate) parallel data, or 4) accept parallel data from either of the two buses and convert the data to serial form. Inputs that control the operations include a single-phase CLOCK (CL), A DATA ENABLE (AE), ASYNCHRONOUS/SYNCHRONOUS (A/ S), A-BUS-TO-B-BUS/B-BUS-TO-A-BUS (A/B), and PARALLEL/ SERIAL (P/S). Data inputs include 16 bidirectional parallel data lines of which the eight A data lines are inputs (3-state outputs) and the B data lines are outputs (inputs) depending on the signal level on the A/B input. In addition, an input for SERIAL DATA is also provided. All register stages are master-slave flip-flops with separate master and slave clock inputs generated internally to allow

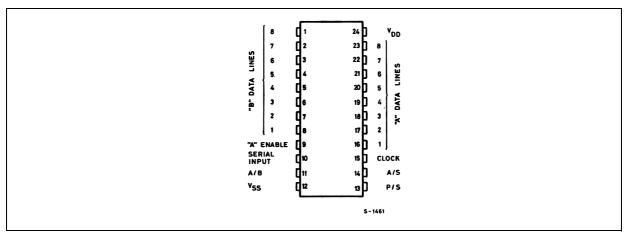

#### **PIN CONNECTION**

September 2002 1/15

synchronous or asynchronous data transfer from master to slave. Isolation from external noise and the effects of loading is provided by output buffering.

PARALLEL OPERATION - A high P/S input signal allows data transfer into the register via the parallel data lines synchronously with the positive transition of the clock, provided the A/S input is low. If the A/S input is high, the transfer is independent of the clock. The direction of data flow is controlled by the A/B input. When this signal is high the A data lines are inputs (and B data lines are outputs); a low A/B signal reverses the direction of data flow. The AE-input is an additional feature which allows many registers to feed data to a common bus. The A DATA lines are

enabled only when this signal is high. Data storage through recirculation of data in each register stage is accomplished by making the A/B signal high and the AE signal low.

SERIAL OPERATION - A low P/S signal allows serial data to transfer into the register synchronously with the positive transition of the clock. The A/S input is internally disabled when the register is in the serial mode (asynchronous serial operation is not allowed). The serial data appears as output data on either the B lines (when A/B is high) or the A lines (when A/B is low and the AE signal is high). Register expansion can be accomplished by simply cascading HCC/HCF4034B packages.

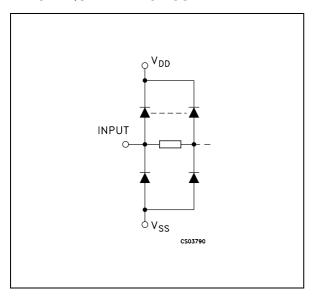

### **IINPUT EQUIVALENT CIRCUIT**

#### **PIN DESCRIPTION**

| PIN No                               | SYMBOL          | NAME AND FUNCTION                                    |

|--------------------------------------|-----------------|------------------------------------------------------|

| 8, 7, 6, 5, 4,<br>3, 2, 1            | 1 to 8          | B Data Lines                                         |

| 16, 17, 18,<br>19, 20, 21,<br>22, 23 | 1 to 8          | A Data Lines                                         |

| 9                                    | AE              | "A" Data Enable                                      |

| 15                                   | CL              | Clock Input                                          |

| 10                                   | SERIAL<br>INPUT | Serial Data input                                    |

| 11                                   | A/B             | "A" Bus to "B" Bus or "B"<br>Bus to "A" Bus Selector |

| 13                                   | P/S             | Parallel/Serial Selector                             |

| 14                                   | A/S             | Asynchronous/Synchronous Selector                    |

| 12                                   | $V_{SS}$        | Negative Supply Voltage                              |

| 24                                   | $V_{DD}$        | Positive Supply Voltage                              |

### **FUNCTIONAL DIAGRAM**

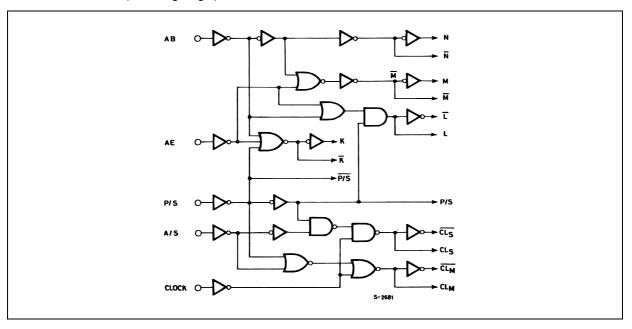

# LOGIC DIAGRAM (Steering Logic)

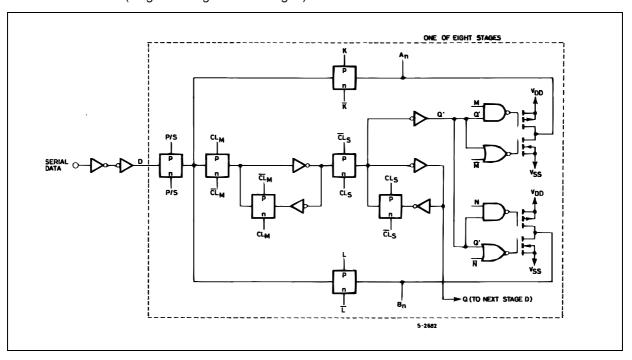

# LOGIC DIAGRAM (Register Stage 1 Of 8 Stages)

TRUTH TABLE (of the register stage)

|                   | INPUTS            |   |   |  |  |  |  |

|-------------------|-------------------|---|---|--|--|--|--|

| CL <sub>M</sub> * | CL <sub>S</sub> * | D | Q |  |  |  |  |

|                   | L                 | L | L |  |  |  |  |

|                   |                   | L | L |  |  |  |  |

|                   |                   | L | • |  |  |  |  |

|                   |                   | X | L |  |  |  |  |

|                   | 7                 | Н | Н |  |  |  |  |

|                   |                   | Н | Н |  |  |  |  |

| 7                 | L                 | Н | • |  |  |  |  |

X : Don't Care

\* : Level Change

• : Invalid Condition

## TRUTH TABLE FOR REGISTER INPUT-LEVELS AND RESULTING REGISTER OPERATION

| "A"<br>Enable | P/S | A/B | A/S | OPERATION*                                                                                            |

|---------------|-----|-----|-----|-------------------------------------------------------------------------------------------------------|

| L             | L   | L   | Х   | Serial Mode; Synch. Serial Data Input, "A" Parallel Data Outputs Disabled                             |

| L             | L   | Н   | Х   | Serial Mode; Synch. Serial Data Input, "B" Parallel Data Output                                       |

| L             | Н   | L   | L   | Parallel Mode; "B" Synch. Parallel Data Inputs, "A" Parallel Data Outputs Disabled                    |

| L             | Н   | L   | Н   | Parallel Mode; "B" Asynch. Parallel Data Inputs, "A" Parallel Data Outputs Disabled                   |

| L             | Н   | Н   | L   | Parallel Mode; "A" Parallel Data Input Disabled, "B" Parallel Data Output, Synch. Data Recirculation  |

| L             | Н   | Н   | Н   | Parallel Mode; "A" Parallel Data Input Disabled, "B" Parallel Data Output, Asynch. Data Recirculation |

| Н             | L   | L   | Х   | Serial Mode; Synch. Serial Data Input, "A" Parallel Data Output                                       |

| Н             | L   | Н   | Х   | Serial Mode; Synch. Serial Data Input, "B" Parallel Data Output                                       |

| Н             | Н   | L   | L   | Parallel Mode; "B" Synch. Parallel Data Input, "A" Parallel Data Output                               |

| Н             | Н   | L   | Н   | Parallel Mode; "B" Asynch. Parallel Data Input, "A" Parallel Data Output                              |

| Н             | Н   | Н   | L   | Parallel Mode; "A" Synch. Parallel Data Input, "B" Parallel Data Output                               |

| Н             | Н   | Н   | Ι   | Parallel Mode; "A" Asynch. Parallel Data Input, "B" Parallel Data Output                              |

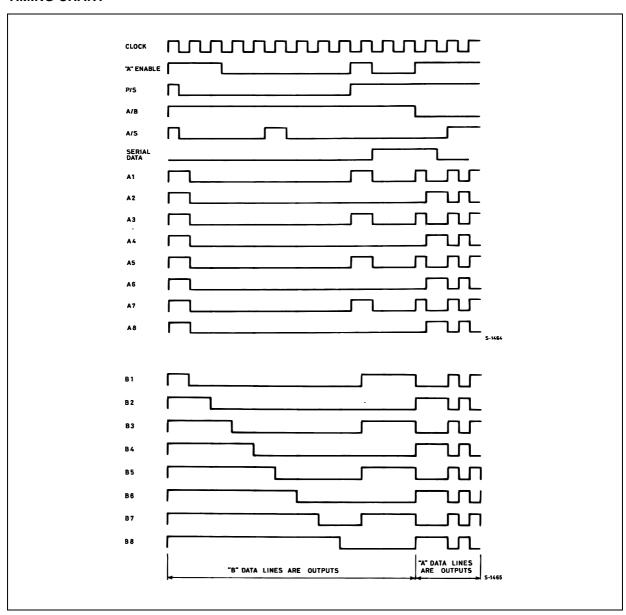

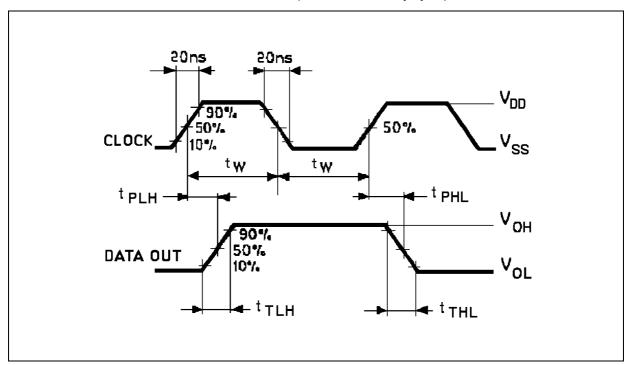

### **TIMING CHART**

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                               | Value                         | Unit |

|------------------|-----------------------------------------|-------------------------------|------|

| $V_{DD}$         | Supply Voltage                          | -0.5 to +22                   | V    |

| VI               | DC Input Voltage                        | -0.5 to V <sub>DD</sub> + 0.5 | V    |

| l <sub>l</sub>   | DC Input Current                        | ± 10                          | mA   |

| P <sub>D</sub>   | Power Dissipation per Package           | 200                           | mW   |

|                  | Power Dissipation per Output Transistor | 100                           | mW   |

| T <sub>op</sub>  | Operating Temperature                   | -55 to +125                   | °C   |

| T <sub>stg</sub> | Storage Temperature                     | -65 to +150                   | °C   |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied.

All voltage values are referred to V<sub>SS</sub> pin voltage.

## **RECOMMENDED OPERATING CONDITIONS**

| Symbol          | Parameter             | Value                | Unit |

|-----------------|-----------------------|----------------------|------|

| $V_{DD}$        | Supply Voltage        | 3 to 20              | V    |

| V <sub>I</sub>  | Input Voltage         | 0 to V <sub>DD</sub> | V    |

| T <sub>op</sub> | Operating Temperature | -55 to 125           | °C   |

## **DC SPECIFICATIONS**

|                 |                                   |      | Test Con       | dition         |          | Value |                       |      |        |      |        |       |       |

|-----------------|-----------------------------------|------|----------------|----------------|----------|-------|-----------------------|------|--------|------|--------|-------|-------|

| Symbol          | Parameter                         | VI   | v <sub>o</sub> | I <sub>O</sub> | $V_{DD}$ | Т     | T <sub>A</sub> = 25°C |      | -40 to | 85°C | -55 to | 125°C | Unit  |

|                 |                                   | (V)  | (V)            | <b>(μA)</b>    | (V)      | Min.  | Тур.                  | Max. | Min.   | Max. | Min.   | Max.  |       |

| ΙL              | Quiescent Current                 | 0/5  |                |                | 5        |       | 0.04                  | 5    |        | 150  |        | 150   |       |

|                 |                                   | 0/10 |                |                | 10       |       | 0.04                  | 10   |        | 300  |        | 300   | ^     |

|                 |                                   | 0/15 |                |                | 15       |       | 0.04                  | 20   |        | 600  |        | 600   | μΑ    |

|                 |                                   | 0/20 |                |                | 20       |       | 0.08                  | 100  |        | 3000 |        | 3000  |       |

| V <sub>OH</sub> | High Level Output                 | 0/5  |                | <1             | 5        | 4.95  |                       |      | 4.95   |      | 4.95   |       |       |

|                 | Voltage                           | 0/10 |                | <1             | 10       | 9.95  |                       |      | 9.95   |      | 9.95   |       | V     |

|                 |                                   | 0/15 |                | <1             | 15       | 14.95 |                       |      | 14.95  |      | 14.95  |       |       |

| $V_{OL}$        | Low Level Output                  | 5/0  |                | <1             | 5        |       | 0.05                  |      |        | 0.05 |        | 0.05  |       |

|                 | Voltage                           | 10/0 |                | <1             | 10       |       | 0.05                  |      |        | 0.05 |        | 0.05  | V     |

|                 |                                   | 15/0 |                | <1             | 15       |       | 0.05                  |      |        | 0.05 |        | 0.05  |       |

| $V_{IH}$        | High Level Input                  |      | 0.5/4.5        | <1             | 5        | 3.5   |                       |      | 3.5    |      | 3.5    |       |       |

|                 | Voltage                           |      | 1/9            | <1             | 10       | 7     |                       |      | 7      |      | 7      |       | V     |

|                 |                                   |      | 1.5/13.5       | <1             | 15       | 11    |                       |      | 11     |      | 11     |       |       |

| $V_{IL}$        | Low Level Input                   |      | 4.5/0.5        | <1             | 5        |       |                       | 1.5  |        | 1.5  |        | 1.5   |       |

|                 | Voltage                           |      | 9/1            | <1             | 10       |       |                       | 3    |        | 3    |        | 3     | V     |

|                 |                                   |      | 13.5/1.5       | <1             | 15       |       |                       | 4    |        | 4    |        | 4     |       |

| $I_{OH}$        | Output Drive                      | 0/5  | 2.5            | <1             | 5        | -1.36 | -3.2                  |      | -1.1   |      | -1.1   |       |       |

|                 | Current                           | 0/5  | 4.6            | <1             | 5        | -0.44 | -1                    |      | -0.36  |      | -0.36  |       | mA    |

|                 |                                   | 0/10 | 9.5            | <1             | 10       | -1.1  | -2.6                  |      | -0.9   |      | -0.9   |       | 111/1 |

|                 |                                   | 0/15 | 13.5           | <1             | 15       | -3.0  | -6.8                  |      | -2.4   |      | -2.4   |       |       |

| $I_{OL}$        | Output Sink                       | 0/5  | 0.4            | <1             | 5        | 0.44  | 1                     |      | 0.36   |      | 0.36   |       |       |

|                 | Current                           | 0/10 | 0.5            | <1             | 10       | 1.1   | 2.6                   |      | 0.9    |      | 0.9    |       | mΑ    |

|                 |                                   | 0/15 | 1.5            | <1             | 15       | 3.0   | 6.8                   |      | 2.4    |      | 2.4    |       |       |

| l <sub>l</sub>  | Input Leakage<br>Current          | 0/18 | Any In         | put            | 18       |       | ±10 <sup>-5</sup>     | ±0.1 |        | ±1   |        | ±1    | μΑ    |

| l <sub>oz</sub> | 3-State Output<br>Leakage Current | 0/18 | Any In         | put            | 18       |       | ±10 <sup>-4</sup>     | ±0.4 |        | ±12  |        | ±12   | μΑ    |

| Cl              | Input Capacitance                 |      | Any In         | put            |          |       | 5                     | 7.5  |        |      |        |       | pF    |

The Noise Margin for both "1" and "0" level is: 1V min. with  $V_{DD}$ =5V, 2V min. with  $V_{DD}$ =10V, 2.5V min. with  $V_{DD}$ =15V

# $\textbf{DYNAMIC ELECTRICAL CHARACTERISTICS} \; (\textbf{T}_{amb} = 25^{\circ} \textbf{C}, \;\; \textbf{C}_{L} = 50 \text{pF}, \; \textbf{R}_{L} = 200 \text{K}\Omega, \;\; \textbf{t}_{f} = \textbf{t}_{f} = 20 \; \text{ns})$

| Symbol                                         | _                         |                     | Test Condition | ,    | Value (*) |      |     |  |

|------------------------------------------------|---------------------------|---------------------|----------------|------|-----------|------|-----|--|

| Symbol                                         | Parameter                 | V <sub>DD</sub> (V) |                | Min. | Тур.      | Max. |     |  |

| t <sub>PHL</sub> t <sub>PLH</sub>              | Propagation Delay Time    | 5                   |                |      | 350       | 700  |     |  |

|                                                | A (B) Parallel Data In to | 10                  |                |      | 120       | 240  | ns  |  |

|                                                | B (A) Parallel Data Out   | 15                  |                |      | 85        | 170  |     |  |

| t <sub>PLZ</sub> t <sub>PHZ</sub>              | 3-State Propagation Delay | 5                   |                |      | 200       | 400  |     |  |

| $t_{PZL}t_{PZH}$                               | Time A/B or AE to "A" OUT | 10                  |                |      | 80        | 160  | ns  |  |

|                                                |                           | 15                  |                |      | 60        | 120  |     |  |

| t <sub>THL</sub> t <sub>TLH</sub>              | Transition Time           | 5                   |                |      | 100       | 200  |     |  |

|                                                |                           | 10                  |                |      | 50        | 100  | ns  |  |

|                                                |                           | 15                  |                |      | 40        | 80   |     |  |

| t <sub>setup</sub> Data Set-Up Time Serial     | 5                         |                     |                | 80   | 160       |      |     |  |

| ·                                              | Data to Clock             | 10                  |                |      | 30        | 60   | ns  |  |

|                                                |                           | 15                  |                |      | 20        | 40   |     |  |

| t <sub>setup</sub>                             | Data Set-Up Time Parallel | 5                   |                |      | 25        | 50   |     |  |

| ·                                              | Data to Clock             | 10                  |                |      | 15        | 30   | ns  |  |

|                                                |                           | 15                  |                |      | 10        | 20   |     |  |

| t <sub>W</sub>                                 | High-level Pulse Width,   | 5                   |                |      | 175       | 350  |     |  |

|                                                | AE, P/S, A/S              | 10                  |                |      | 70        | 140  | ns  |  |

|                                                |                           | 15                  |                |      | 40        | 80   |     |  |

| f <sub>CL</sub>                                | Maximum Clock             | 5                   |                | 2    | 4         |      |     |  |

|                                                | Frequency                 | 10                  |                | 5    | 10        |      | MHz |  |

|                                                |                           | 15                  |                | 7    | 14        |      |     |  |

| t <sub>W</sub>                                 | Clock Pulse Width         | 5                   |                |      | 125       | 250  |     |  |

|                                                |                           | 10                  |                |      | 50        | 100  | ns  |  |

|                                                |                           | 15                  |                |      | 35        | 70   |     |  |

| t <sub>r</sub> , t <sub>f</sub> <sup>(1)</sup> | Clock Input Rise or Fall  | 5                   |                |      |           | 15   |     |  |

| 1 / 1                                          | Time                      | 10                  |                |      |           | 15   | μs  |  |

| İ                                              |                           | 15                  |                |      |           | 15   | 1   |  |

<sup>(\*)</sup> Typical temperature coefficient for all V<sub>DD</sub> value is 0.3 %/°C

(1): If more than one unit is cascaded. tr should be made less than or equal to the sum of the transition time and the fixed propagation delay of the output of the driving stage for the estimated capacitive load.

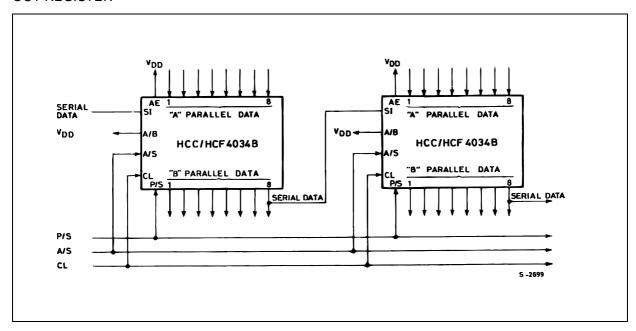

### **TYPICAL APPLICATIONS**

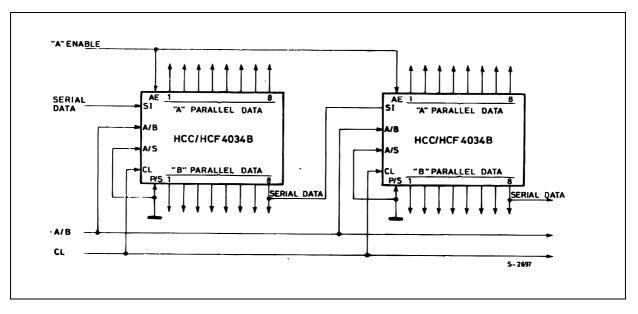

16 BIT PARALLEL IN/PARALLEL OUT PARALLEL IN/SERIAL IN PARALLEL OUT, SERIAL IN/SERIAL OUT REGISTER

# 16 BIT SERIAL IN/GATED PARALLEL OUT REGISTER

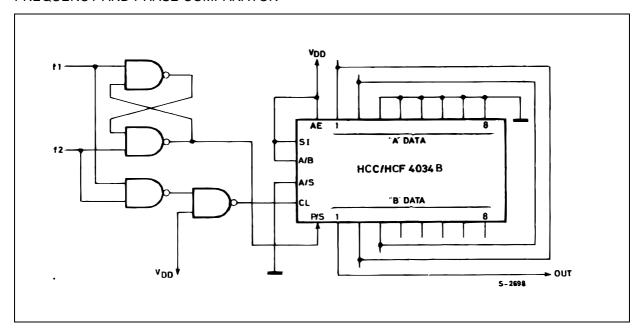

### FREQUENCY AND PHASE COMPARATOR

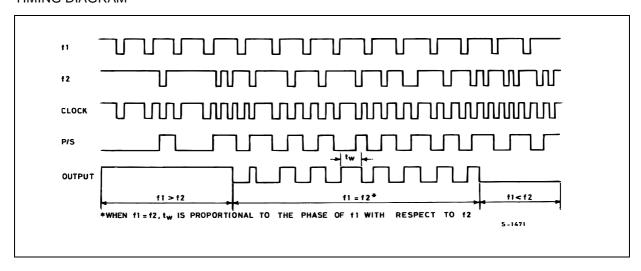

### **TIMING DIAGRAM**

**57**

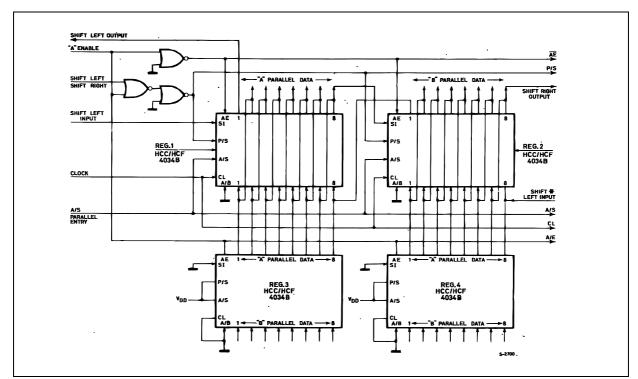

### SHIFT RIGHT/SHIFT LEFT WITH PARALLEL INPUTS

A "High" ("Low") on the Shift Left/Shift Right input allows serial data on the Shift Left Input (Shift Right Input) to enter the register on the positive transition of the clock signal. A "high" on the "A" Enable Input disables the "A" parallel data lines on Reg. 1 and 2 and enables the "A" data lines on registers 3 and 4 and allows parallel data into

registers 1 and 2. Other logics schemes may be used in place of registers 3 and 4 for parallel loading. When parallel inputs are not used Reg. 3 and 4 and associated logic are not required.

\* Shift Left input must be disabled during parallel entry.

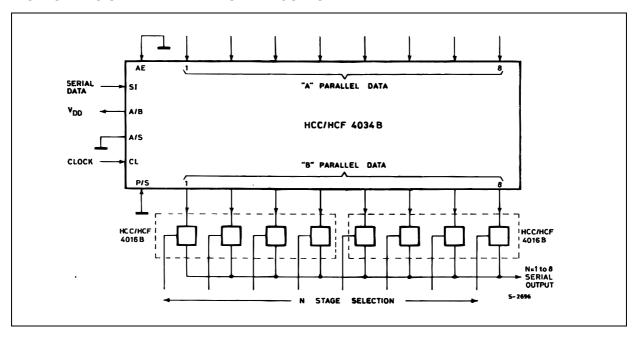

### N-STAGE REGISTER WITH FIXED SERIAL OUTPUT LINE

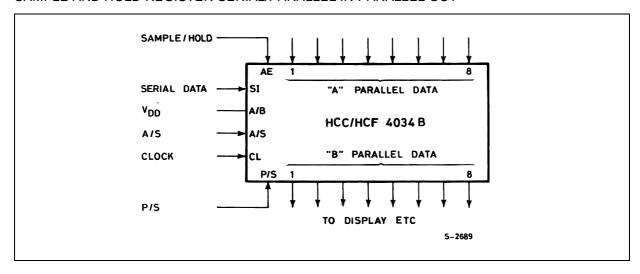

## SAMPLE AND HOLD REGISTER-SERIAL/PARALLEL IN-PARALLEL OUT

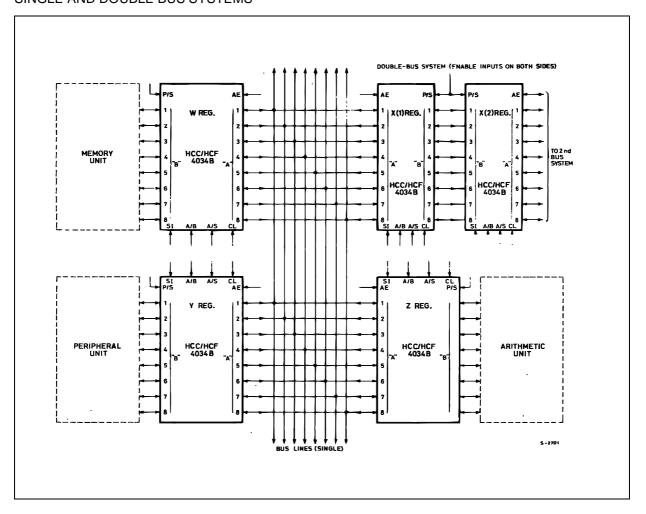

# SINGLE AND DOUBLE BUS SYSTEMS

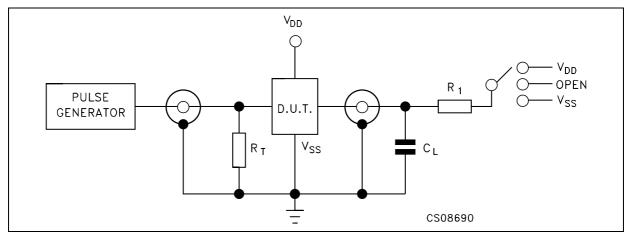

### **TEST CIRCUIT**

| TEST                                | SWITCH          |

|-------------------------------------|-----------------|

| t <sub>PLH</sub> , t <sub>PHL</sub> | Open            |

| t <sub>PZL</sub> , t <sub>PLZ</sub> | $V_{DD}$        |

| t <sub>PZH</sub> , t <sub>PHZ</sub> | V <sub>SS</sub> |

C<sub>L</sub> = 50pF or equivalent (includes jig and probe capacitance)

# WAVEFORM: PROPAGATION DELAY TIMES (f=1MHz; 50% duty cycle)

$R_L = 200 K\Omega$

$R_T = Z_{OUT}$  of pulse generator (typically 50 $\Omega$ )

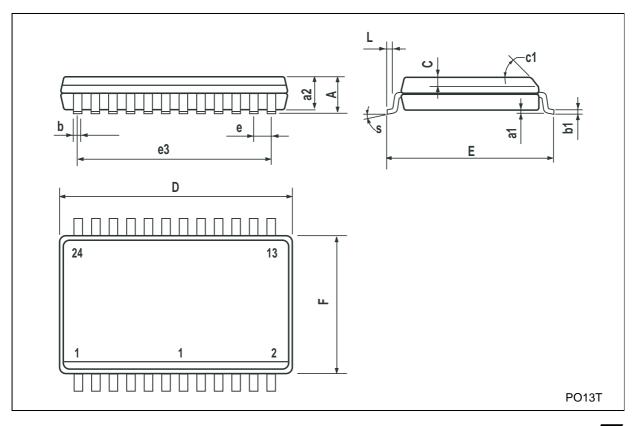

# **SO-24 MECHANICAL DATA**

| DIM.   |       | mm.   |       | inch   |       |       |  |  |

|--------|-------|-------|-------|--------|-------|-------|--|--|

| DIIVI. | MIN.  | TYP   | MAX.  | MIN.   | TYP.  | MAX.  |  |  |

| А      |       |       | 2.65  |        |       | 0.104 |  |  |

| a1     | 0.1   |       | 0.2   | 0.004  |       | 0.008 |  |  |

| a2     |       |       | 2.45  |        |       | 0.096 |  |  |

| b      | 0.35  |       | 0.49  | 0.014  |       | 0.019 |  |  |

| b1     | 0.23  |       | 0.32  | 0.009  |       | 0.012 |  |  |

| С      |       | 0.5   |       |        | 0.020 |       |  |  |

| c1     |       |       | 45°   | (typ.) |       | •     |  |  |

| D      | 15.20 |       | 15.60 | 0.598  |       | 0.614 |  |  |

| E      | 10.00 |       | 10.65 | 0.393  |       | 0.419 |  |  |

| е      |       | 1.27  |       |        | 0.050 |       |  |  |

| e3     |       | 13.97 |       |        | 0.550 |       |  |  |

| F      | 7.40  |       | 7.60  | 0.291  |       | 0.300 |  |  |

| L      | 0.50  |       | 1.27  | 0.020  |       | 0.050 |  |  |

| S      |       |       | 8° (1 | max.)  | •     | •     |  |  |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

© The ST logo is a registered trademark of STMicroelectronics

# © 2002 STMicroelectronics - Printed in Italy - All Rights Reserved STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco Singapore - Spain - Sweden - Switzerland - United Kingdom - United States.

© http://www.st.com