MAY 1994

DS3005-2.0

# **ZN425E8** 8-BIT D-A/A-D CONVERTER

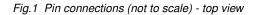

The ZN425 is a monolithic 8-bit D-A converter containing an R-2R ladder network of diffused resistors with precision bipolar switches, and in addition a counter and a 2.5V precision voltage reference. The counter is a powerful addition which allows a precision staircase to be generated very simply by clocking the counter.

## **FEATURES**

- $\blacksquare$   $\pm^{1}/_{2}$  LSB Linearity Error

- $0^{\circ}C$  to +70°C

- TTL and 5V CMOS Compatible

- Single +5V Supply

- Settling Time (D-A) 1µs Typical

- Conversion Time (A-D) 1ms Typical, using Ramp and Compare Technique

- Extra Components Required

D-A: Reference Capacitor (Direct Voltage Output through 10kOhms Typ.)

A-D: Comparator, Gate, Clock and Reference Capacitor

#### **ORDERING INFORMATION**

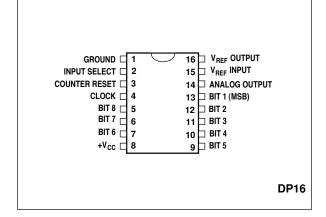

Ambient operating temperature 0°C to +70°C PackageDP16

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply voltage, V <sub>CC</sub>                 | +7.0V            |

|-------------------------------------------------|------------------|

| Max. voltage, logic and V <sub>REF</sub> inputs | +5.5V See note 3 |

| Operating temperature range                     | 0°C to +70°C     |

| Storage temperature range                       | -55°C to +125°C  |

# ZN425

ELECTRICAL CHARACTERISTICS (at  $T_{amb}$  = 25°C and  $V_{CC}$  = +5V unless otherwise stated)

# INTERNAL VOLTAGE REFERENCE

| Parameter                                | Symbol           | Min. | Тур. | Max. | Units  | Conditions           |

|------------------------------------------|------------------|------|------|------|--------|----------------------|

| Output voltage                           | V <sub>REF</sub> | 2.4  | 2.55 | 2.7  | V      | I = 7.5mA (internal) |

| Slope resistance                         | R <sub>S</sub>   | -    | 2    | 4    | Ω      | I = 7.5mA (internal) |

| V <sub>REF</sub> temperature coefficient |                  | -    | 40   | -    | ppm/°C | I = 7.5mA (internal) |

NOTE: The internal reference requires a  $0.22\mu$ F stabilising capacitor between pins 1 and 16.

# 8-BIT D-A CONVERTER AND COUNTER

| Parameter                                             | Symbol          | Min.  | Тур.  | Max.  | Units  | Conditions                                   |

|-------------------------------------------------------|-----------------|-------|-------|-------|--------|----------------------------------------------|

| Resolution                                            |                 | 8     | -     | -     | bits   |                                              |

| Non-linearity                                         |                 | -     | -     | ±0.5  | LSB    | see note 3                                   |

| Differential non-linearity                            |                 | -     | ±0.5  | -     | LSB    | see note 6                                   |

| Settling time                                         |                 | -     | 1.0   | -     | μs     | 1LSB step                                    |

| Settling time to 0.5LSB                               |                 | -     | 1.5   | 2.5   | μs     | All bits ON to OFF<br>or OFF to ON           |

| Offset voltage ZN425E8                                | V <sub>OS</sub> | -     | 3     | 8     | mV     | All bits OFF<br>See note 3                   |

| Full-scale output                                     |                 | 2.545 | 2.550 | 2.555 | V      | All bits ON<br>Ext. V <sub>REF</sub> = 2.56V |

| Full-scale temp. coefficient                          |                 | -     | 3     | -     | ppm/°C | Ext. V <sub>REF</sub> = 2.56V                |

| Linearity error temp.coeff.                           |                 | -     | 7.5   | -     | ppm/°C | relative to F.S.R.                           |

| Analog output resistance                              | R <sub>O</sub>  | -     | 10    | -     | kΩ     |                                              |

| External reference voltage                            |                 | 0     | -     | 3.0   | V      |                                              |

| Supply voltage                                        | V <sub>CC</sub> | 4.5   | -     | 5.5   | V      | See note 3                                   |

| Supply current                                        | ۱ <sub>S</sub>  | -     | 25    | 35    | mA     |                                              |

| High level input voltage                              | V <sub>IH</sub> | 2.0   | -     | -     | V      | See notes 1 and 2                            |

| Low level input voltage                               | VIL             | -     | -     | 0.7   | V      |                                              |

| High level input current                              | IIH             | -     | -     | 10    | μA     | $V_{CC} = max.$<br>$V_{I} = 2.4V$            |

|                                                       |                 | -     | -     | 100   | μA     | $V_{CC} = max.$<br>$V_{I} = 5.5V$            |

| Low level input current bit inputs                    | IIL             | -     | -     | -6.8  | mA     | $V_{CC} = max.$<br>$V_{I} = 0.3V$            |

| Low level input current, clock reset and input select | ΙL              | -     | -     | -0.18 | mA     |                                              |

### ELECTRICAL CHARACTERISTICS (cont.)

| Parameter                          | Symbol          | Min. | Тур. | Max. | Units | Conditions                                     |

|------------------------------------|-----------------|------|------|------|-------|------------------------------------------------|

| High level output current          | I <sub>ОН</sub> | -    | -    | -40  | μΑ    |                                                |

| Low level output current           | I <sub>OL</sub> | -    | -    | 1.6  | mA    |                                                |

| High level output voltage          | V <sub>OH</sub> | 2.4  | -    | -    | V     | $V_{CC} = min. Q = 1$<br>$I_{load} = -40\mu A$ |

| Low level output voltage           | V <sub>OL</sub> | -    | -    | 0.4  | V     | $V_{CC} = min. Q = 0$<br>$I_{load} = 1.6mA$    |

| Maximum counter clock<br>frequency | f <sub>c</sub>  | 3    | 5    | -    | MHz   | See note 5                                     |

| Reset pulse width                  | t <sub>R</sub>  | 200  | -    | -    | ns    | See note 4                                     |

NOTES:

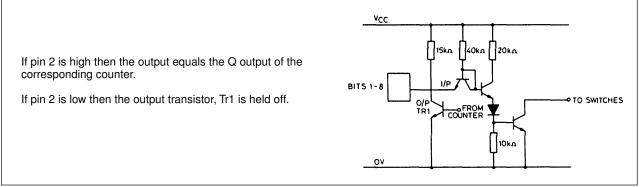

1. The input select pin (2) must be held low when bit pins (5, 6, 7, 9, 10,11,12, and 13) are driven externally.

2. To obtain counter outputs on bit pins the select pin (2) should be taken to  $+V_{CC}$  via a 1k $\Omega$  resistor.

3. (a) Maximum operating voltage. Between 70°C and 125°C the maximum supply voltage is reduced to 5.0V.

(b) Offset voltage. The difference is due to package lead resistance. This offset will normally be removed by the setting up procedure, and because the offset temperature coefficient is low, the specified accuracy will be maintained.

4. The device may be reset by gating from its own counter. 5.  $F_{max}$  in A-D mode is 300kHz, see Operating Note 2.

6. Monotonic over full operating temperature range.

#### INTRODUCTION

The ZN425 is an 8-bit dual mode D-A/A-D converter. It contains an 8-bit D-A converter using an advanced design of R-2R ladder network and an array of precision bipolar switches plus an 8-bit binary counter and a 2.5V precision voltage reference all on a single monolithic chip.

The special design of the ladder network results in full 8-bit accuracy using normal diffused resistors.

The use of the on-chip voltage reference is pin optional to retain flexibility. An external fixed or varying reference may therefore be substituted.

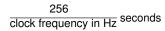

By including an 8-bit binary counter on the chip, A-D conversion can be obtained simply by adding an external comparator (LM311) and clock inhibit gating (7400).

By simply clocking the counter the ZN425 can be used as a self-contained precision ramp generator. A logic input select switch is incorporated which determines whether the precision switches accept the outputs from the binary counter or external digital inputs depending upon whether the control signal is respectively high or low.

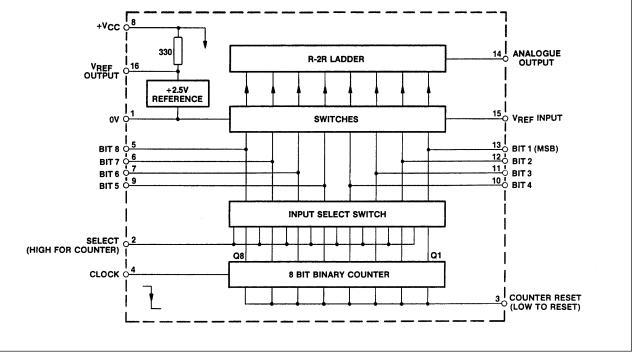

The converter is of the voltage switching type and uses an R-2R resistor ladder network as shown in Fig.3.

Each 2R element is connected either to 0V or  $V_{REF}$  by transistor switches specially designed for low offset voltage (typically 1mV).

Binary weighted voltages are produced at the output of the R-2R ladder, the value depending on the digital number applied to the bit inputs.

Fig.3 The R-2R ladder network

## ZN425

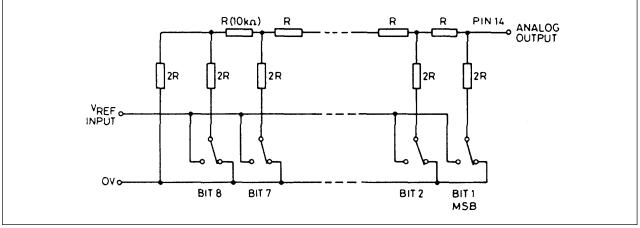

Fig.4 Bit inputs/outputs

# **OPERATING NOTES**

#### 1.8-bit D-A Converter

The ZN425 gives an analog voltage output directly from pin 14 therefore the usual current to voltage converting amplifier is not required. The output voltage drift, due to the temperature coefficient of the analog output resistance  $R_O$ , will be less than 0.004% per °C (or 1LSB/100°C) if  $R_L$  is chosen to be  $\geq 650 k \Omega$ .

In order to remove the offset voltage and to calibrate the converter a buffer amplifier is necessary. Fig.5 shows a typical scheme using the internal reference voltage. To minimise temperature drift in this and similar applications the source resistance to the inverting input of the operational amplifier should be approximately  $6k\Omega.$  The calibration procedure is as follows:

- i. Set all bits to OFF (low) and adjust  $R_2$  until  $V_{OUT}$  = 0.000V.

- ii. Set all bits to ON (high) and adjust  $R_1$  until  $V_{OUT}$  = Nominal full-scale reading 1LSB

- iii. Repeat i. and ii.

Fig.5 8-bit D-A converter

#### ZN425

#### 2. 8-bit A-D Converter

A counter type ADC can be constructed by adding a voltage comparator and a latch as in Fig.6. On the negative edge of the CONVERT COMMAND pulse (15µs minimum) the counter is set to zero and the STATUS latch to logical 1.On the positive edge the gate is opened, enabling clock pulses to be fed to the counter input of the ZN425. The minimum negative clock pulse width of the ZN425 is 100ns. The analog output of the ZN425 ramps until it equals the voltage on the other input of the comparator. At this point the comparator output goes low and resets the STATUS to inhibit further clock pulses. The logical 0 from the status latch indicates that the 8-bit digital output is a valid representation of the analog input voltage.

A small capacitor of 47pF is added to the ZN425 output to stop any positive going glitches prematurely resetting the status latch. This capacitance is in parallel with the ZN425 output capacitance (20-30pF) and they form a time constant with the ZN425 output resistance ( $10k\Omega$ ). This time constant is the main limit to the maximum clock frequency. With a fast comparator the clock frequency can be up to 300kHz. The conversion time varies with the input being a maximum for full-scale input.

Maximum conversion time =

Fig.6 8-bit A-D converter

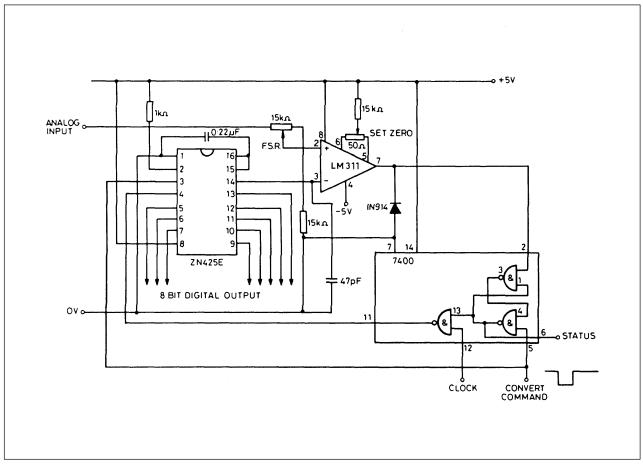

#### 3. Precision Ramp generator

The inclusion of an 8-bit binary counter on the chip gives the ZN425 a useful ramp generator function. The circuit, Fig. 7, uses the same buffer stages as the D-A converter. The calibration procedure is also the same. Holding pin 2 low will set all bits to ON and if RESET is taken low with pin 2 high all the bits are turned OFF. If the end voltages of the ramp are not required to be set accurately then the buffer stage could be omitted and the voltage ramp will appear directly at pin 14.

Fig.7 Precision ramp generator

HEADQUARTERS OPERATIONS GEC PLESSEY SEMICONDUCTORS Cheney Manor, Swindon, Wiltshire, United Kingdom. SN2 2QW Tel: (01793) 518000 Fax: (01793) 518411

#### GEC PLESSEY SEMICONDUCTORS

P.O. Box 660017,

1500 Green Hills Road,

Scotts Valley, California 95067-0017,

United States of America.

Tel (408) 438 2900

Fax: (408) 438 5576

CUSTOMER SERVICE CENTRES

- FRANCE & BENELUX Les Ulis Cedex Tel: (1) 64 46 23 45 Fax: (1) 64 46 06 07

- GERMANY Munich Tel: (089) 3609 06-0 Fax: (089) 3609 06-55

- ITALY Milan Tel: (02) 66040867 Fax: (02)66040993

- **JAPAN** Tokyo Tel: (03) 5276-5501 Fax: (03) 5276-5510

- **JAFAN** 10ky0 1el. (03) 3270-3301 1 ax. (03) 3270-3310

- NORTH AMERICA Scotts Valley, USA Tel: (408) 438 2900 Fax: (408) 438 7023

- SOUTH EAST ASIA Singapore Tel: (65) 3827708 Fax: (65) 3828872

- SWEDEN Stockholm Tel: 46 8 702 97 70 Fax: 46 8 640 47 36

- TAIWAN, ROC Taipei Tel: 886 2 5461260 Fax: 886 2 7190260

- UK, EIRE, DENMARK, FINLAND & NORWAY

- Swindon Tel: (01793) 518510 Fax: (01793) 518582

These are supported by Agents and Distributors in major countries world-wide.

© GEC Plessey Semiconductors 1994 Publication No. DS3005 Issue No. 2.0 May 1994 TECHNICAL DOCUMENTATION - NOT FOR RESALE. PRINTED IN UNITED KINGDOM

This publication is issued to provide information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. The Company reserves the right to alter without prior knowledge the specification, design or price of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be salisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information on data used is up to date and has not been superseded. These products are not suitabile for use in any medical products whose failure to perform may result in eliminary death to the user. All products and materials are solid and particles are split and the structure of table. Which was a validable on concernet of table which was a validable on concernet.

#### ZN425