## Product Preview

# NTSC/PAL Chroma 10 Color TV and Timebase Processor

The MC13017 consists of all the necessary circuits for TV NTSC/PAL decoding and timebase processing. It forms a kit set with the MC44301 VIF and the TDA3190 Sound IF and Power for a low cost, high performance CTV system.

- On-Chip Sync Separator

- Dual Loop Horizontal Timebase

- Direct Locked Vertical Counter

- X-Ray Protection

- Noise Blanking on Sync Separator

- NTSC/PAL Color Decoding

- Direct Interface with SECAM TDA3030B

- 4.43/3.579 MHz Crystal Reference

- Three DC High Impedance Control Outputs for Contrast, Brightness, and Saturation

- 12 V Supply

- Vertical Ramp Buffer Output

- Sandcastle Output

- Hue Control

## NTSC/PAL CHROMA 10 COLOR TV and TIMEBASE PROCESSOR

SEMICONDUCTOR TECHNICAL DATA

| PIN CONNECTIONS         |    |         |                     |  |

|-------------------------|----|---------|---------------------|--|

| V <sub>CC3</sub>        | 1  | <u></u> | V <sub>CC2</sub>    |  |

| V. Gnd                  | 2  | 39      | H. Gnd              |  |

| V. Feedback             | 3  | 38      | H. O/P              |  |

| V. Out                  | 4  | 37      | PD2                 |  |

| Buffer Ramp             | 5  | 36      | H. Flyback          |  |

| Ramp Cap                | 6  | 35      | PD1                 |  |

| V. Height               | 7  | 34      | H. Freq             |  |

| Sync Sep Cap            | 8  | 33      | X–Ray               |  |

| Sync I/P                | 9  | 32      | Contrast            |  |

| Luma I/P                | 10 | 31      | Brightness          |  |

| V <sub>CC1</sub> + 12 V | 11 | 30      | Sandcastle<br>Pulse |  |

| Hue                     | 12 | 29      | R O/P               |  |

| Chroma I/P              | 13 | 28      | G O/P               |  |

| ACC                     | 14 | 27      | B O/P               |  |

| DL E                    | 15 | 26      | DC Ref & BL         |  |

| DL C                    | 16 | 25      | Gnd                 |  |

| Sat                     | 17 | 24      | Xtal FB             |  |

| ID                      | 18 | 23      | Xtal Drive          |  |

| V I/P                   | 19 | 22      | VCO FLT             |  |

| U I/P                   | 20 | 21      | 90° FLT             |  |

| (Top View)              |    |         |                     |  |

#### **ORDERING INFORMATION**

| Device   | Operating<br>Temperature Range | Package     |

|----------|--------------------------------|-------------|

| MC13017P | $T_A = 0^\circ$ to +70°C       | Plastic DIP |

#### **MAXIMUM RATINGS** ( $T_A = 25^{\circ}C$ , unless otherwise noted.)

| Rating                                               | Symbol                                                  | Value        | Unit |

|------------------------------------------------------|---------------------------------------------------------|--------------|------|

| Power Supply Voltages                                | V <sub>CC1</sub> , V <sub>CC3</sub><br>V <sub>CC2</sub> | 15<br>10     | V    |

| Operating Temperature Range                          | T <sub>A</sub>                                          | 0 to +70     | 5C   |

| Storage Temperature Range                            | T <sub>stg</sub>                                        | - 55 to +125 | °C   |

| Horizontal Output Voltage<br>Vertical Output Voltage | Voh<br>Vov                                              | 8.0<br>4.0   | V    |

## **PIN FUNCTION DESCRIPTION**

| Pin      | Function                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|----------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1        | V <sub>CC3</sub>           | +12 V supply for V <sub>CC2</sub> power regulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 2        | Vert Gnd                   | Vertical output analog ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 3        | Vert Feedback              | The Ramp on Pin 6 is internally inverted, level shifted and subtracted from the input to Pin 3. The result appears as an output on an open collector at Pin 4.                                                                                                                                                                                                                                                                                                                                        |  |

| 4        | Vert Out                   | Vertical ramp output to external vertical power drive.                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 5        | Buffer Ramp                | The vertical buffer ramp output of Pin 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 6        | Ramp Cap                   | The external cap is charged by a current controlled through vertical height control Pin 7 to produce a vertical ramp. The discharge of the cap is controlled internally by the vertical counter.                                                                                                                                                                                                                                                                                                      |  |

| 7        | Vert Height                | Current input for vertical height control.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 8, 9     | Sync Sep Cap,<br>Sync I/P  | Sync separator input is a NPN transistor stage with the signal presented at its base with a peak level of about 4.0 V. The emitter is brought out to Pin 8 through a 200 $\Omega$ resistor so that a capacitor with a series resistor may be connected. The circuit behaves as a peak detector with a slicing level controlled by the choice of charge and discharge resistors. An additional time constant is connected through a diode to prevent the slice level from riding up on the field sync. |  |

| 11       | V <sub>CC1</sub>           | +12 V supply for chroma.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 12       | Hue                        | This is Hue control for NTSC system. It should be connected to V <sub>CC1</sub> at PAL system. When voltage at Pin 12 is smaller than 8.0 V, NTSC mode is selected.                                                                                                                                                                                                                                                                                                                                   |  |

| 15       | DL E                       | Delay line drive open emitter terminal.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 16       | DL C                       | Delay line drive open collector terminal.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 18       | ID Filter                  | An external filter cap is connected at this pin for ID circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 19, 20   | V, U                       | V, U inputs after delay line to detectors.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 21       | 90° Filter                 | 90° phase shifter filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 22       | VCO Filter                 | Color reference VCO filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 23<br>24 | Xtal 2<br>Xtal 1           | A 4.43 MHz (PAL), or 3.579 MHz (NTSC) crystal is connected to the internal VCO for color subcarrier reference frequency.                                                                                                                                                                                                                                                                                                                                                                              |  |

| 30       | Sandcastle<br>Pulse Output | The Sandcastle Pulse Output is delivered through 200 $\Omega$ from an emitter–follower with 10 k $\Omega$ pull–down. The blanking duration is determined by the applied flyback pulse. The burst gate determined by the second half of the flyback levels are: Blanking (4.0 V), Burst Gate (11 V).                                                                                                                                                                                                   |  |

| 35       | PD1                        | Horizontal phase detector current output. The PLL 1 is locked to the sync input with 2H oscillator.                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 36       | Horiz Flyback              | Horizontal flyback, a positive input pulse exceeded threshold of 1.0 V is required, input impedance is between 600 and 2.0 k $\Omega$ so that a minimum of 0.5 mA current is needed to exceed the threshold voltage. The recommended peak current is 2.0 mA.                                                                                                                                                                                                                                          |  |

| 37       | PD2                        | Second horizontal phase detector current output. The function of PLL 2 is to adjust the horizontal drive in order to maintain the flyback in phase with the oscillator.                                                                                                                                                                                                                                                                                                                               |  |

| 38       | Horiz Out                  | This is a saturated NPN transistor with a 2.0 k\Omega internal load to regulate supply V <sub>CC2</sub> .                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 39       | Horiz Gnd                  | Horizontal analog output grounding should be connected nearby the external horizontal output stage.                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 40       | V <sub>CC2</sub>           | Regulated supply to horizontal timebase section. A diode is in series with 270 $\Omega$ from V <sub>CC3</sub> + 12 V to block the high voltage startup supply of 10 mA for horizontal oscillator.                                                                                                                                                                                                                                                                                                     |  |

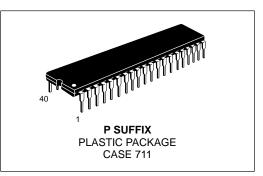

## **OUTLINE DIMENSIONS**

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and **M** are registered trademarks of Motorola, Inc. Is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

USA/EUROPE: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. 1–800–441–2447 JAPAN: Nippon Motorola Ltd.; Tatsumi–SPD–JLDC, Toshikatsu Otsuki, 6F Seibu–Butsuryu–Center, 3–14–2 Tatsumi Koto–Ku, Tokyo 135, Japan. 03–3521–8315

MFAX: RMFAX0@email.sps.mot.com – TOUCHTONE (602) 244–6609 INTERNET: http://Design-NET.com

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.