April 1998

LF353 Wide Bandwidth Dual JFET Input Operational Amplifier

# National Semiconductor

# LF353 Wide Bandwidth Dual JFET Input Operational Amplifier

#### **General Description**

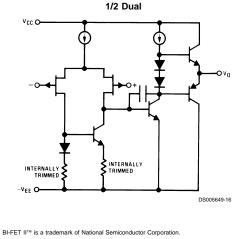

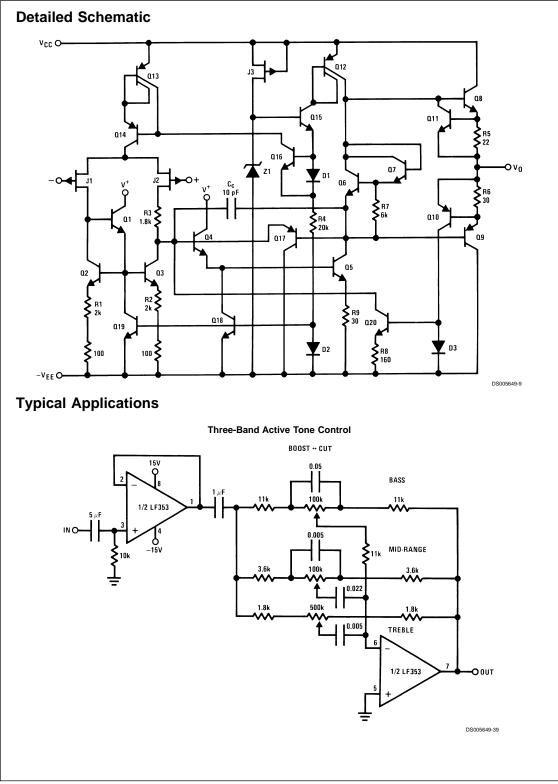

These devices are low cost, high speed, dual JFET input operational amplifiers with an internally trimmed input offset voltage (BI-FET II<sup>™</sup> technology). They require low supply current yet maintain a large gain bandwidth product and fast slew rate. In addition, well matched high voltage JFET input devices provide very low input bias and offset currents. The LF353 is pin compatible with the standard LM1558 allowing designers to immediately upgrade the overall performance of existing LM1558 and LM358 designs.

These amplifiers may be used in applications such as high speed integrators, fast D/A converters, sample and hold circuits and many other circuits requiring low input offset voltage, low input bias current, high input impedance, high slew rate and wide bandwidth. The devices also exhibit low noise and offset voltage drift.

### Features

- Internally trimmed offset voltage: 10 mV

- Low input bias current: 50pA

- Low input noise voltage: 25 nV/√Hz

- Low input noise current: 0.01  $pA/\sqrt{Hz}$

- Wide gain bandwidth: 4 MHz

- High slew rate: 13 V/µs

- Low supply current: 3.6 mA

- High input impedance: 10<sup>12</sup>Ω

- Low total harmonic distortion A<sub>v</sub>=10,: <0.02% RL=10k, V<sub>O</sub>=20Vp-p, BW=20 Hz-20 kHz

- Low 1/f noise corner: 50 Hz

- Fast settling time to 0.01%: 2 µs

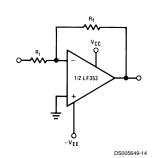

## **Typical Connection**

# Simplified Schematic

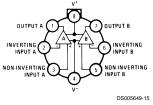

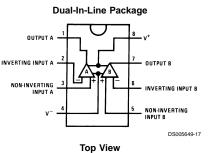

## **Connection Diagrams**

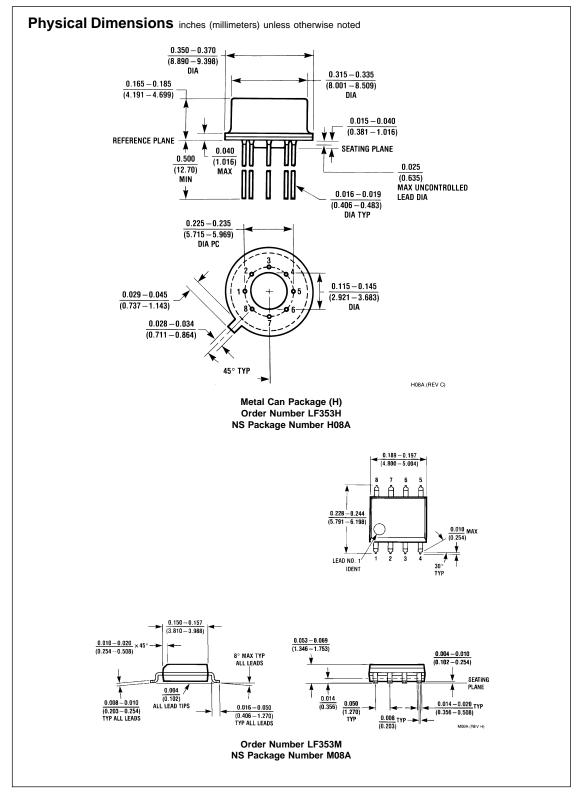

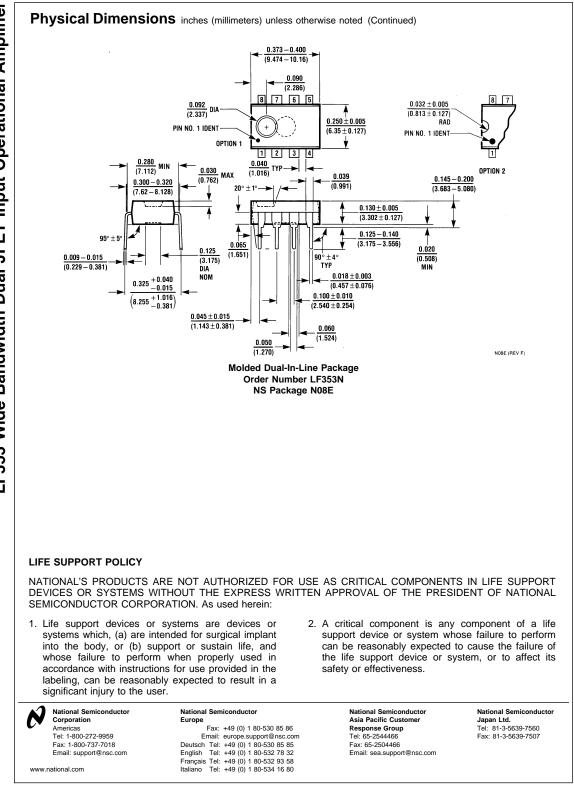

#### Metal Can Package

Top View Order Number LF353H See NS Package Number H08A

Order Number LF353M or LF353N See NS Package Number M08A or N08E

### Absolute Maximum Ratings (Note 1)

.

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage                              | ±18V            |

|---------------------------------------------|-----------------|

| Power Dissipation                           | (Note 2)        |

| Operating Temperature Range                 | 0°C to +70°C    |

| T <sub>j</sub> (MAX)                        | 150°C           |

| Differential Input Voltage                  | ±30V            |

| Input Voltage Range (Note 3)                | ±15V            |

| Output Short Circuit Duration               | Continuous      |

| Storage Temperature Range                   | –65°C to +150°C |

| Lead Temp. (Soldering, 10 sec.)             | 260°C           |

| Soldering Information                       |                 |

| Dual-In-Line Package<br>Soldering (10 sec.) | 260°C           |

| Small Outline Package                                                                                                                                                                                                                                                                           |                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Vapor Phase (60 sec.)                                                                                                                                                                                                                                                                           | 215°C                                                                       |

| Infrared (15 sec.)                                                                                                                                                                                                                                                                              | 220°C                                                                       |

| See AN-450 "Surface Mounting Methods a<br>on Product Reliability" for other methods o<br>surface mount devices.                                                                                                                                                                                 |                                                                             |

| ESD Tolerance (Note 8)                                                                                                                                                                                                                                                                          | 1700V                                                                       |

| θ <sub>JA</sub> M Package                                                                                                                                                                                                                                                                       | TBD                                                                         |

| Note 1: Absolute Maximum Ratings indicate limits beyre<br>the device may occur. Operating ratings indicate conditi<br>vice is functional, but do not guarantee specific perform<br>Characteristics state DC and AC electrical specifications<br>and the public surface according a performance. | ons for which the de-<br>ance limits. Electrical<br>s under particular test |

vice is functional, but do not guarantee specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given, however, the typical value is a good indication of device performance.

# DC Electrical Characteristics (Note 5)

| Symbol                                     | Parameter                          | Conditions                                  | LF353 |                  |     | Units |

|--------------------------------------------|------------------------------------|---------------------------------------------|-------|------------------|-----|-------|

|                                            |                                    |                                             | MIn   | Тур              | Max | 1     |

| V <sub>OS</sub> Input Offset Voltage       | Input Offset Voltage               | R <sub>S</sub> =10kΩ, T <sub>A</sub> =25°C  |       | 5                | 10  | mV    |

|                                            | Over Temperature                   |                                             |       | 13               | mV  |       |

| $\Delta V_{OS} / \Delta T$                 | Average TC of Input Offset Voltage | R <sub>s</sub> =10 kΩ                       |       | 10               |     | µV/°C |

| l <sub>os</sub>                            | DS Input Offset Current            | T <sub>j</sub> =25°C, (Notes 5, 6)          |       | 25               | 100 | pА    |

|                                            |                                    | T <sub>j</sub> ≤70°C                        |       |                  | 4   | nA    |

| I <sub>B</sub>                             | Input Bias Current                 | T <sub>j</sub> =25°C, (Notes 5, 6)          |       | 50               | 200 | pА    |

|                                            |                                    | T <sub>j</sub> ≤70°C                        |       |                  | 8   | nA    |

| R <sub>IN</sub>                            | Input Resistance                   | T <sub>j</sub> =25°C                        |       | 10 <sup>12</sup> |     | Ω     |

| A <sub>VOL</sub> Large Signal Voltage Gain | Large Signal Voltage Gain          | V <sub>S</sub> =±15V, T <sub>A</sub> =25°C  | 25    | 100              |     | V/mV  |

|                                            |                                    | $V_{O}$ =±10V, R <sub>L</sub> =2 k $\Omega$ |       |                  |     |       |

|                                            |                                    | Over Temperature                            | 15    |                  |     | V/mV  |

| Vo                                         | Output Voltage Swing               | $V_{S}$ =±15V, R <sub>L</sub> =10k $\Omega$ | ±12   | ±13.5            |     | V     |

| V <sub>CM</sub>                            | Input Common-Mode Voltage          | V <sub>S</sub> =±15V                        | ±11   | +15              |     | V     |

|                                            | Range                              |                                             |       | -12              |     | V     |

| CMRR                                       | Common-Mode Rejection Ratio        | R <sub>S</sub> ≤ 10kΩ                       | 70    | 100              |     | dB    |

| PSRR                                       | Supply Voltage Rejection Ratio     | (Note 7)                                    | 70    | 100              |     | dB    |

| I <sub>s</sub>                             | Supply Current                     |                                             |       | 3.6              | 6.5 | mA    |

# AC Electrical Characteristics

| Symbol         | Parameter                       | Conditions                                               | LF353 |      |     | Units  |

|----------------|---------------------------------|----------------------------------------------------------|-------|------|-----|--------|

|                |                                 |                                                          | Min   | Тур  | Max | 1      |

|                | Amplifier to Amplifier Coupling | T <sub>A</sub> =25°C, f=1 Hz–20 kHz                      |       | -120 |     | dB     |

|                |                                 | (Input Referred)                                         |       |      |     |        |

| SR             | Slew Rate                       | V <sub>S</sub> =±15V, T <sub>A</sub> =25°C               | 8.0   | 13   |     | V/µs   |

| GBW            | Gain Bandwidth Product          | V <sub>S</sub> =±15V, T <sub>A</sub> =25°C               | 2.7   | 4    |     | MHz    |

| e <sub>n</sub> | Equivalent Input Noise Voltage  | T <sub>A</sub> =25°C, R <sub>S</sub> =100Ω,<br>f=1000 Hz |       | 16   |     | nV/√Hz |

| i <sub>n</sub> | Equivalent Input Noise Current  | T <sub>j</sub> =25°C, f=1000 Hz                          |       | 0.01 |     | pA/√Hz |

Note 2: For operating at elevated temperatures, the device must be derated based on a thermal resistance of 115°C/W typ junction to ambient for the N package, and 158°C/W typ junction to ambient for the H package.

#### AC Electrical Characteristics (Continued)

Note 3: Unless otherwise specified the absolute maximum negative input voltage is equal to the negative power supply voltage.

Note 4: The power dissipation limit, however, cannot be exceeded.

Note 5: These specifications apply for  $V_S=\pm 15V$  and  $0^{\circ}C \le T_A \le +70^{\circ}C$ .  $V_{OS}$ ,  $I_B$  and  $I_{OS}$  are measured at  $V_{CM}=0$ .

Note 6: The input bias currents are junction leakage currents which approximately double for every 10°C increase in the junction temperature,  $T_j$ . Due to the limited production test time, the input bias currents measured are correlated to junction temperature. In normal operation the junction temperature rises above the ambient temperature as a result of internal power dissipation, P<sub>D</sub>.  $T_j=T_A+\theta_{jA} P_D$  where  $\theta_{jA}$  is the thermal resistance from junction to ambient. Use of a heat sink is recommended if input bias current is to be kept to a minimum.

Note 7: Supply voltage rejection ratio is measured for both supply magnitudes increasing or decreasing simultaneously in accordance with common practice.  $V_S = \pm 6V$  to  $\pm 15V$ .

Note 8: Human body model, 1.5 k $\Omega$  in series with 100 pF.

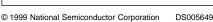

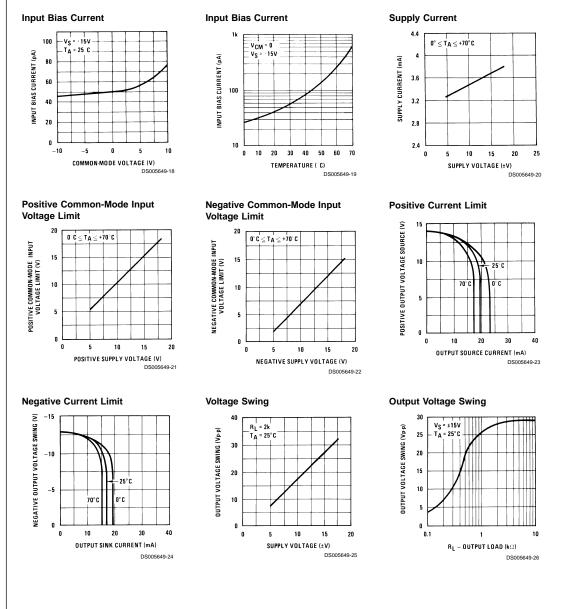

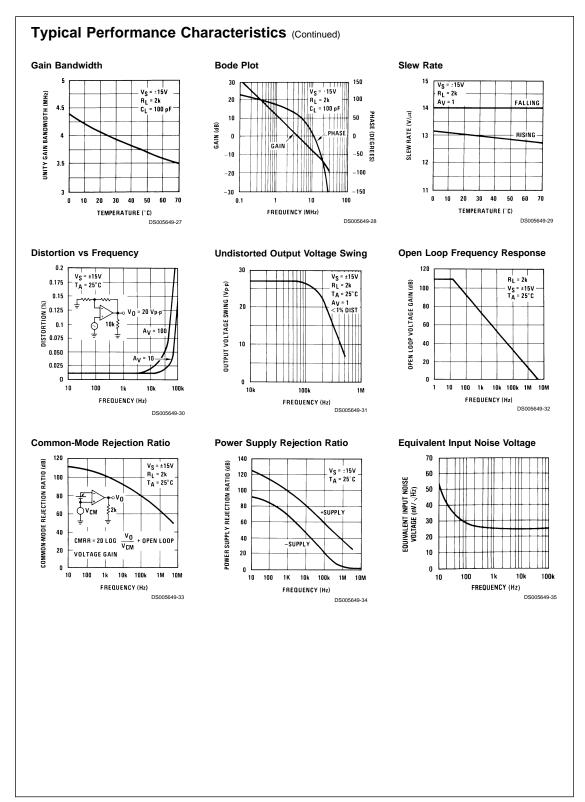

## **Typical Performance Characteristics**

www.national.com

www.national.com

4

DS005649-

### **Application Hints**

These devices are op amps with an internally trimmed input offset voltage and JEET input devices (BI-FET II). These JFETs have large reverse breakdown voltages from gate to source and drain eliminating the need for clamps across the inputs. Therefore, large differential input voltages can easily be accommodated without a large increase in input current. The maximum differential input voltage is independent of the supply voltages. However, neither of the input voltages should be allowed to exceed the negative supply as this will cause large currents to flow which can result in a destroyed unit.

Exceeding the negative common-mode limit on either input will force the output to a high state, potentially causing a reversal of phase to the output. Exceeding the negative common-mode limit on both inputs will force the amplifier output to a high state. In neither case does a latch occur since raising the input back within the common-mode range again puts the input stage and thus the amplifier in a normal operating mode.

Exceeding the positive common-mode limit on a single input will not change the phase of the output; however, if both inputs exceed the limit, the output of the amplifier will be forced to a high state.

The amplifiers will operate with a common-mode input voltage equal to the positive supply; however, the gain bandwidth and slew rate may be decreased in this condition. When the negative common-mode voltage swings to within 3V of the negative supply, an increase in input offset voltage may occur.

Each amplifier is individually biased by a zener reference which allows normal circuit operation on  $\pm 6V$  power supplies. Supply voltages less than these may result in lower gain bandwidth and slew rate.

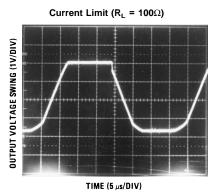

The amplifiers will drive a 2 k $\Omega$  load resistance to ±10V over the full temperature range of 0°C to +70°C. If the amplifier is forced to drive heavier load currents, however, an increase in input offset voltage may occur on the negative voltage swing and finally reach an active current limit on both positive and negative swings.

Precautions should be taken to ensure that the power supply for the integrated circuit never becomes reversed in polarity or that the unit is not inadvertently installed backwards in a socket as an unlimited current surge through the resulting forward diode within the IC could cause fusing of the internal conductors and result in a destroyed unit.

As with most amplifiers, care should be taken with lead dress, component placement and supply decoupling in order to ensure stability. For example, resistors from the output to an input should be placed with the body close to the input to minimize "pick-up" and maximize the frequency of the feedback pole by minimizing the capacitance from the input to ground.

A feedback pole is created when the feedback around any amplifier is resistive. The parallel resistance and capacitance from the input of the device (usually the inverting input) to AC ground set the frequency of the pole. In many instances the frequency of this pole is much greater than the expected 3 dB frequency of the closed loop gain and consequently there is negligible effect on stability margin. However, if the feedback pole is less than approximately 6 times the expected 3 dB frequency a lead capacitor should be placed from the output to the input of the op amp. The value of the added capacitor should be such that the RC time constant of this capacitor and the resistance it parallels is greater than or equal to the original feedback pole time constant.

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.